# Master Thesis in ENGINEERING IN COMPUTER SCIENCE

# Lightweight approximate virtual page access tracing of multi-threaded applications via static binary instrumentation

Advisor

Candidate

Prof. Francesco Quaglia

Simone Economo

Co-Advisor

PhD. Alessandro Pellegrini

Academic Year 2014/2015

#### Acknowledgment

A thesis, be it a bachelor's thesis, a master's thesis or any other form of dissertation, is not a thesis without acknowledgments. First of all, because we should never lose the occasion to thank those we love and esteem. Second, because many theses wouldn't be possible without the professional and emotional support of many different people—this couldn't be more true for my thesis. Last but not least, because they are so damn fun to read. So, here we are!—beware: this chapter makes ridiculous use of italics, don't say I didn't warn you!

My sincere gratitude goes above all to Prof. Francesco Quaglia and Prof. Bruno Ciciani for introducing me to the amazing world of computer architectures and operating systems, and for turning me into a better *engineer* through their wonderful courses. They are undoubtedly inspiring from a professional point of view, but I mostly *admire* them as persons. I also wish to thank PhD Alessandro Pellegrini for his support, especially in the last *crazy* days before the graduation date, and for all the incredibly *nerdy* chats we had between one "segmentation fault" and another.

I owe a big "thank you" to Davide too, a kind friend and colleague. Your help has been *invaluable* to me and I am extremely grateful to you for sacrificing *your* time in my *darkest* hours. I wouldn't be here if it wasn't for you.

I cannot be more grateful to Lorenzo, Marco and Elisa for being the best friends one can ever have. One way or another, you made me feel lucky through your words, thoughts and actions—Marco's langiullate deserve honorable mention... they're memorable! I am proud to have you in my life. Thanks also to Donato, Lorenzo N., Martina and Federica for being a late but extremely welcome addition to this list.

To my friends of the exclusive "Frati Francescani del DIS" club, which also happen to have founded the *coolest* Whatsapp group ever, "Le Panze Sacre", I wish to say: do you already have a schedule ready for next's month list of *sagre* and food festivals?! Jokes apart, thanks for all the amazing moments that we had and, hopefully, will have in future. No, seriously... *sagra del tartufo* anyone?

As for the emotional support, I cannot help but express my deepest gratitude to the people that hold a special spot in my life. My parents, Giancarlo and Ileana, because they have always seconded my decisions and supported my choices in every situation, even when they were a bit... doubtful. I hope to be able to return to you at least a tiny portion of the boundless love that you constantly give to me. My relatives, too, because they made me feel part of a bigger family. Last but not least my second family, Annalisa, Fabrizio and Diana, for teaching me the real meaning of happiness—but also for pleasuring my stomach with delicious food!

Have I forgotten someone? I don't think so... that's all folks, you can stop reading now!

iii

To Claudia, I wish to say more things than I will ever be able to write. We joked on the number of lines that you deserved in the acknowledgments, like if you deserved a number! What you did for me, in these months... since we met, it is something that make me feel loved in a way that is special and unique. I see you as my half and my dearest friend. Someone to protect, but also my strength. You complete me, but also challenge me in all positive ways. You are the proof that a simple heart can be full of unimaginable love, and I'm glad that, six years ago in Aula 16, you decided, completely out of your mind, to take my hand for the first time. Thank you.

# To Alessandra and Orietta, for all the love that you gave to me.

### Contents

| A | ckno             | vledgment                                          |    |  |  |  |

|---|------------------|----------------------------------------------------|----|--|--|--|

| 1 | Inti             | oduction                                           | -  |  |  |  |

| 2 | Inst             | rumentation                                        | ,  |  |  |  |

|   | 2.1              | Hardware instrumentation                           | 8  |  |  |  |

|   | 2.2              | Software instrumentation                           | 6  |  |  |  |

|   |                  | 2.2.1 Static instrumentation                       | 1  |  |  |  |

|   |                  | 2.2.2 Dynamic instrumentation                      | 1  |  |  |  |

|   | 2.3              | Hijacker                                           | 1: |  |  |  |

|   |                  | 2.3.1 Front-end                                    | 1! |  |  |  |

|   |                  | 2.3.2 IBR                                          | 10 |  |  |  |

|   |                  | 2.3.3 Back-end                                     | 19 |  |  |  |

|   | 2.4              | State of the art                                   | 1  |  |  |  |

|   |                  | 2.4.1 PEBIL                                        | 19 |  |  |  |

|   |                  | 2.4.2 DynamoRIO                                    | 2  |  |  |  |

|   |                  | 2.4.3 Pin                                          | 2  |  |  |  |

|   |                  | 2.4.4 Dyninst                                      | 2! |  |  |  |

|   |                  | 2.4.5 Valgrind                                     | 20 |  |  |  |

|   |                  | 2.4.6 Comparison                                   | 28 |  |  |  |

| 3 | Memory Tracing 3 |                                                    |    |  |  |  |

|   | 3.1              | Sampling                                           | 3  |  |  |  |

|   |                  | 3.1.1 Static sampling                              | 33 |  |  |  |

|   |                  | 3.1.2 Dynamic sampling                             | 3  |  |  |  |

|   | 3.2              | Buffering                                          | 3  |  |  |  |

|   | 3.3              | State of the art                                   | 3  |  |  |  |

|   |                  | 3.3.1 MetaSim Tracer                               | 33 |  |  |  |

|   |                  | 3.3.2 Effects of binary instrumentation on tracing | 3' |  |  |  |

|   |                  | 3.3.3 A threading-model for memory tracing         | 39 |  |  |  |

| 4 | Vir              | tual Page Tracing                                  | 42 |  |  |  |

|   | 4.1              | Finding relevant code regions                      | 4  |  |  |  |

|   |                  | 4.1.1 Basic blocks and control flow graph          | 4  |  |  |  |

|   |                  | 4.1.2 Computing basic blocks                       | 4  |  |  |  |

| CONTENTS | vi |

|----------|----|

|----------|----|

|   |     | 4.1.3 Computing program cycles              | 18         |

|---|-----|---------------------------------------------|------------|

|   |     | 4.1.4 Ultimating basic block features 5     | 52         |

|   | 4.2 |                                             | 52         |

|   |     | 4.2.1 Tracing back the section              | 53         |

|   |     | 4.2.2 Tracing back the virtual page 5       | 55         |

|   |     |                                             | 58         |

|   |     |                                             | 58         |

|   |     |                                             | 30         |

|   |     |                                             | 31         |

|   | 4.3 | Contribution to Hijacker                    | 33         |

|   |     |                                             | 34         |

|   |     |                                             | 34         |

| 5 | Exp | erimental Assessment 6                      | 6          |

|   | 5.1 | Worst-case execution time evaluation 6      | 39         |

|   | 5.2 |                                             | 72         |

|   | 5.3 |                                             | 74         |

| 6 | Cor | clusions and Future Work 7                  | <b>'</b> 9 |

|   | 6.1 | Current limitations and future directions 8 | 31         |

|   |     |                                             |            |

# List of Figures

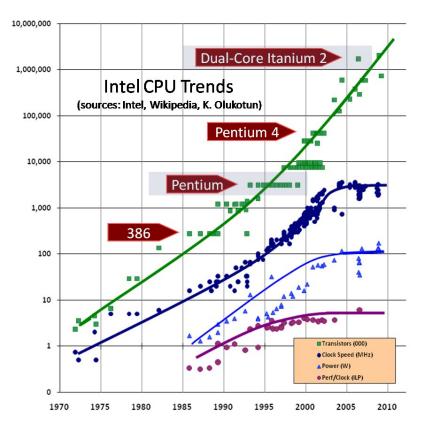

| 1.1  | A pictorial representation of Moore's Law from 1970 to 2010.                | 3  |

|------|-----------------------------------------------------------------------------|----|

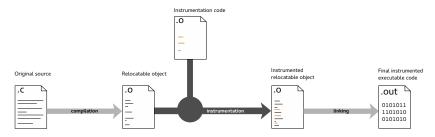

| 2.1  | Hijacker's instrumentation process                                          | 14 |

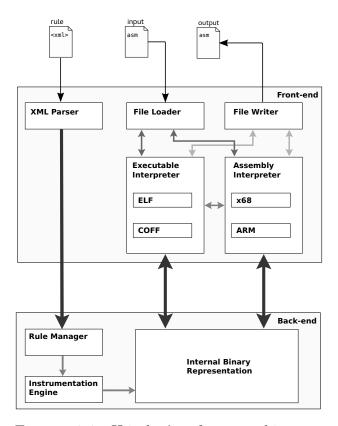

| 2.2  | Hijacker's software architecture                                            | 15 |

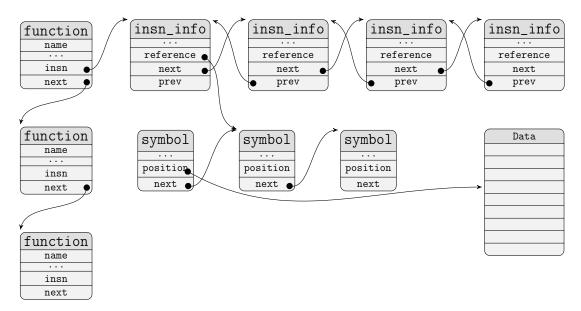

| 2.3  | Hijacker's internal binary representation                                   | 17 |

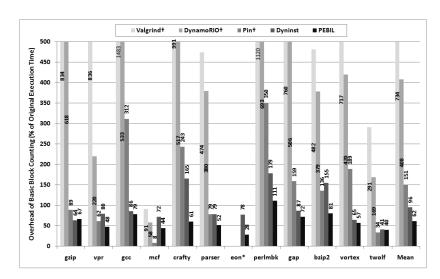

| 2.4  | Performance evaluation of PEBIL with respect to other instrumentation tools | 22 |

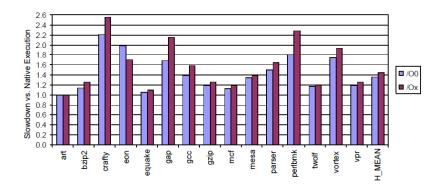

| 2.5  | Performance evaluation of DynamoRIO with no dynamic optimization            | 23 |

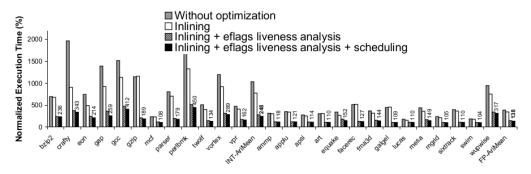

| 2.6  | Performance evaluation of Pin alone with and without optimizations          | 24 |

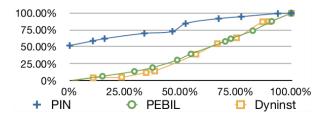

| 2.7  | Evaluation of the proportionality metric for Pin, PEBIL and                 |    |

|      | Dyninst                                                                     | 26 |

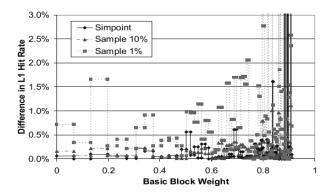

| 3.1  | Evaluation of the cache hit rate estimation error produced                  |    |

|      | by SimPoint-based sampling                                                  | 37 |

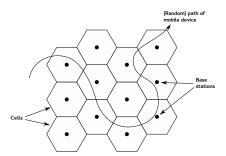

| 5.1  | GSM area network example                                                    | 66 |

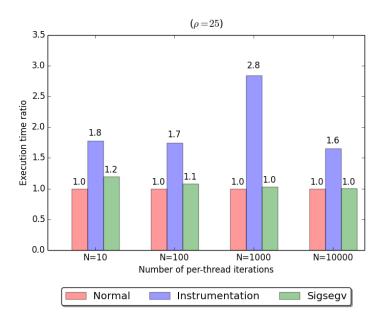

| 5.2  | Execution time evaluation in the worst-case with $\rho=25\%$                | 71 |

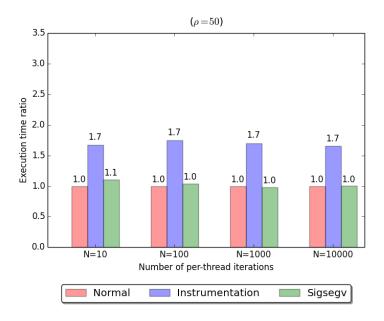

| 5.3  | Execution time evaluation in the worst-case with $\rho = 50\%$ .            | 71 |

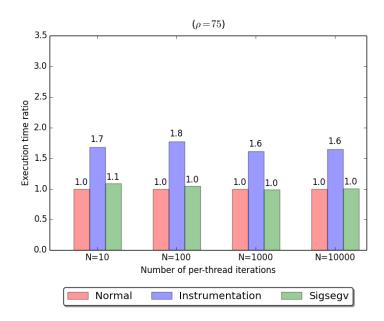

| 5.4  | Execution time evaluation in the worst-case with $\rho = 75\%$ .            | 72 |

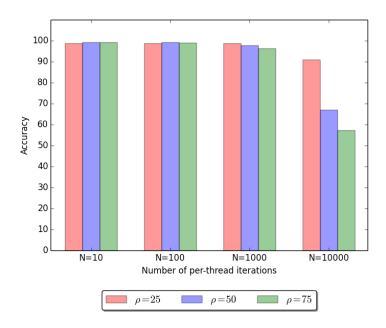

| 5.5  | Accuracy evaluation in the best-case                                        | 73 |

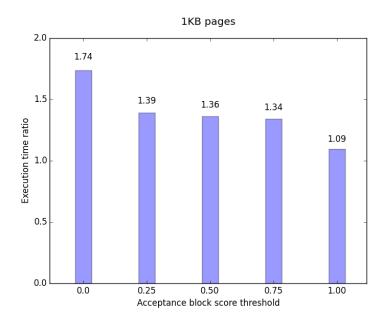

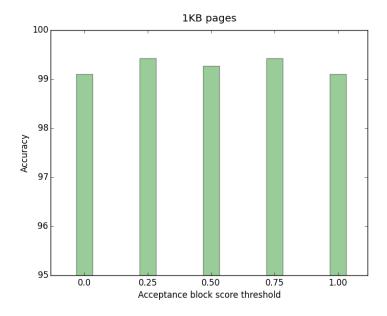

| 5.6  | Trade-off efficiency evaluation when $\mathcal{H} = 1$ KB                   | 76 |

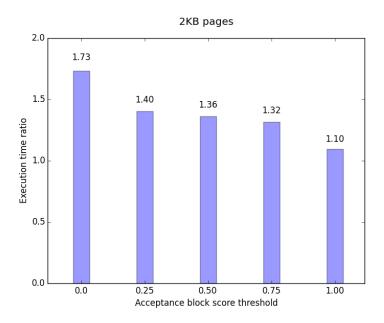

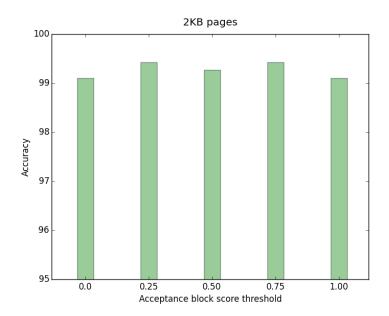

| 5.7  | Trade-off efficiency evaluation when $\mathcal{H} = 2KB$                    | 76 |

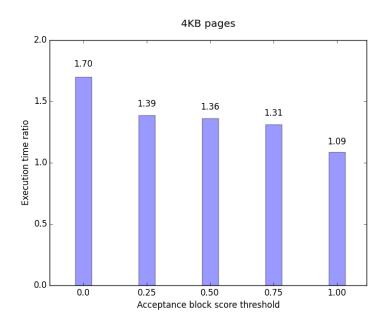

| 5.8  | Trade-off efficiency evaluation when $\mathcal{H} = 4KB$                    | 77 |

| 5.9  | Trade-off accuracy evaluation when $\mathcal{H} = 1$ KB                     | 77 |

| 5.10 | Trade-off accuracy evaluation when $\mathcal{H}=2KB$                        | 78 |

| 5.11 | Trade-off accuracy evaluation when $\mathcal{H} = 4KB$                      | 78 |

### List of Tables

| 2.1 | A comparison of binary instrumentation tools                | 29 |

|-----|-------------------------------------------------------------|----|

| 3.1 | MetaSim Tracer collection time and prediction accuracy com- |    |

|     | parison using trace sampling                                | 35 |

| 3.2 | MetaSim Tracer collection time and prediction accuracy com- |    |

|     | parison using an upper sampling limit on block traversal    | 35 |

| 3.3 | MetaSim Tracer collection time and prediction accuracy com- |    |

|     | parison using basic block hotness                           | 35 |

| 3.4 | A comparison of memory address trace collection only for    |    |

|     | different binary instrumentation tools                      | 41 |

| 5.1 | Access counts for the scheduling and processing functions   |    |

|     | when $N = 10000$                                            | 74 |

## List of Algorithms

| 4.1 | Block splitting algorithm        | 47 |

|-----|----------------------------------|----|

| 4.2 | Program cycle detection: phase 1 | 49 |

| 4.3 | Program cycle detection: phase 2 | 51 |

| 4.4 | Program cycle detection: phase 3 | 51 |

# CHAPTER 1

#### Introduction

If the auto industry advanced as rapidly as the semiconductor industry, a Rolls Royce would get half a million miles per gallon, and it would be cheaper to throw it away than to park it.

— Gordon Moore (1998, attributed)

Computing architectures are complex. In the early days of computing, systems were simple. When it was clear that the original design could not provide anymore the performance guarantees and the functional capabilities demanded by industry, such design underwent a change. On the one hand, the need for accelerated computer graphics resulted into dedicated graphic cards, bundling special-purpose cores with support for unconventional operations that can offload most of the floating-point-intensive tasks from the main processor. On the other hand, the demand for powerful portable devices with long-lasting batteries caused small power-efficient cores to be placed side by side on the same chip with large high-performance ones. Nowadays we have computing systems which are powerful and highly performing, but also able to consume as little energy as needed to meet economical constraints. Moreover, they are heterogeneous, meaning that their ability to work at different performance and power level requirements is provided by a wide spectrum of complementary components, each possessing different operational capabilities and peculiarities.

The road to heterogeneous systems was driven not only by industry pressure, but also by physical constraints, i.e. 'walls' that deflected the expected course of evolution of computing architectures in an unforeseeable, yet fascinating way. The power wall, historically speaking, is the first of such walls. It states that individual computing units cannot be made faster without violating the limits imposed by fundamental physics via the power equation [1]:

$$P_{DD} = \alpha \cdot CV_{DD}^2 f_{av} \tag{1.1}$$

In the above equation,  $P_{DD}$  represents the average dynamic power dis-

sipated by a single CMOS transistor in response to an input change. When the input value switches from high to low or vice versa, the internal capacitance needed to keep the circuit output stable gets charged or discharged. For this reason, the above quantity depends on the capacitance load C, the supply voltage that drives the circuit  $V_{DD}$  and the average frequency of input events  $f_{av}$ . Additionally, an activity factor  $\alpha$  is included to represent the probability that the circuit's internal capacitance state will switch upon an input event.

Clearly, the higher the power dissipated by a transistor, the higher the heat which is eventually radiated as a by-product, which in turns requires more powerful (and expensive) cooling techniques. As we can see from equation 1.1, the only way to decrease the dynamic power  $P_{DD}$  consumed by a circuit is by decreasing the value of all other quantities involved. However, a decrease in the value of  $f_{av}$  means a slower clock rate which, in turns, yields a slower system. Therefore, to benefit from higher clock rates without affecting the dissipated power, C and  $V_{DD}$  must decrease.

If we look at Moore's Law [2], we observe that from 1970 to 2004 the number of transistors in a computing system doubled roughly every 18 to 24 months, while the clock rate increased every 34 months (see figure 1.1). These trends can be explained by virtue of the power equation, since a decrease in transistors size means a decrease in load capacitance. Hence, by scaling down the size of transistors, processor manufacturers were able to provide more horsepower at the same or slightly increase consumption of power and heat radiation. At the same time, by reducing the supply voltage of circuits, faster clock rates were possible. Over time, Moore's Law turned into a self-fulfilling prophecy, driven by hardened competition and the demand for faster processors.

Unfortunately, circuit sizes and supply voltage cannot be driven arbitrarily down. The leakage current which is responsive for the static power consumption component of circuits becomes more and more influential as transistors shrink. Moreover, circuits become more and more sensible to interfering signals as supply voltage approaches the same order of magnitude as noise. Eventually, one cannot make transistors smaller or supply voltage lower, while also increasing the clock rate and keeping dynamic power consumption below acceptable thresholds. One of them must be sacrificed.

This led to the concept of *multi-core* systems, i.e. computing architectures where multiple processing units are present and operate in a parallel fashion, at a lower individual clock speed than single-core systems but providing overall an increased computing power. By giving up individual clock speed, the process of scaling down the size of transistors can continue. Besides scaling in the vertical direction, increasing the number of processing units allows to increase the overall number of transistors by virtue of hori-

FIGURE 1.1: A pictorial representation of Moore's Law from 1970 to 2010.

zontal scaling, thus keeping up with Moore's Law.

The memory wall is another of such figurative walls. Due to technological constraints, processor speed began to increase at a faster rate than memory bandwidth. This ever-increasing imbalance turned out to drastically hamper the performance of even highly-optimized scientific applications [3]. As a result of this trend, processors started to bundle smaller and faster memories closer to their cores, the so-called caches. The introduction of cache memories was an important breakthrough for computing architectures, since for the first time it invalidated the statement that all memory accesses are equal. Nowadays, the concept of memory caches is so pervasive that additional memory layers were gradually added, resulting into what is referred to as the memory hierarchy.

Similarly to the power wall, the *coherency wall* has been hit not so ago. It results from increasing the number of cores and the raw storage capacity in a system up to a point where: (a) it becomes economically prohibitive to maintain an unified shared-memory model with growing storage; (b) cache-level synchronization protocols are the main source of bottleneck for programs.

On the one hand, large-capacity memory banks are still too expensive to produce with the current manufacturing technology. They are easily defeated by summing up the capacities of smaller and cheaper memory banks. By grouping cores in clusters and spreading such memory banks in such a way that each cluster has its own memory banks, memory access latency for local requests can be kept low to the detriment of remote accesses which are more costly. Moreover, this allows the system to spread accesses across different physical storage components, thus reducing contention at memory buses. This is the model adopted by NUMA architectures (Non-Uniform Memory Access) [4].

On the other hand, the presence of a high number of cores, hence of many disjoint cache memories, poses challenges to any synchronization scheme aimed at enforcing data consistency. Many-core systems with a single memory bus usually implement a bus snooping protocol. According to this scheme, every write request on a private cache memory produces a broadcast event on the bus which forces all other caches targeted by the update to invalidate their lines. For read requests that produce a cache miss, a request message is also broadcast. This kind of architectural scheme would not work in a many-core scenario because of the high probability of contention at the interconnection level, even with the presence of multiple memory banks and buses.

For this reason, many-core platforms implement the directory-based protocol. Whenever a core loads a cache line in its private cache, it registers itself into a shared global directory. In this directory, for every cache line, there's a list of registered cores that expect to be notified upon a change on that line, by means of an invalidation message, or a read request. This mechanism scales better than the snooping bus, but it can still create contention at the various interconnection buses if the number of cores that share a line increase. For this reason, cache-incoherent architectures are being studied where coherency of cached data along different clusters is not automatically enforced by the firmware [5].

This thesis studies an ancient but still relevant problem in computer science. Namely, the detection of the memory access pattern exhibited by generic applications—both single-threaded and multi-threaded ones. Memory access traces have several applications both for performance and profiling purposes. As an example, traces can be used together with a simulation environment to assess the degree to which the application is able to efficiently interact with the underlying memory hierarchy of the architecture, as complex as it can be. The same kind of traces can also be used to guide hardware design, in the long run, so as to more closely match the behavior of a desired class of scientific applications.

Actually, the work presented in this thesis is a specialization of tracing

to virtual pages. To the best of my knowledge, virtual page access tracing is a novel problem in the literature which, like generic memory tracing, has many interesting applications. In the heterogeneous systems scenario, tracing of virtual pages can be used to dynamically move data in a NUMA architecture closer to the cluster where the thread is actually running, or moving the thread closer to the NUMA node where its working set is actually residing [6] [7]. To this extent, the target application can be both a generic multi-threaded program or an application that runs on top of a custom middleware, such as an optimistic simulation platform [8]. In this case, moving data closer to a thread means tracing the state of a simulation object not only to migrate it, but also logging it into a close memory bank to support efficient rollback mechanisms [9].

The key technique to accomplish virtual page access tracing is binary instrumentation, which is a way to transparently execute additional logic at run-time without affecting the actual application-level behavior coded by the programmer. Historically, instrumentation has been seen as a tool for debugging and profiling purposes. Nonetheless, general-purpose instrumentation is starting to emerge in the literature as the means to implement any sort of additional logic, apart from that bound to maintenance and monitoring tasks. Notice that instrumentation tends to work at the application-level, thus leaving unaltered the library and operating system levels. This allows instrumentation tools to work 'out of the box', without any modification to the compilation tool-chain, the standard library environment or the operating system. However, it is natural to look at the problem the other way round—namely, from the point of view of the standard library and the OS. Even as instrumentation requires no adjustment at these levels and other consolidated development tools, these layers and tools alone can provide virtually the same services as instrumentation. Furthermore, they can do it with the same or even higher degree of transparency of instrumentation—since no additional compilation pass to the application must be made,—provided that we're prone to developing patches for them. The naturally rising dilemma is hence to choose one approach or the other, aware of the benefits and drawbacks that come along with this choice.

To this extent, my work makes extensive use of instrumentation to the detriment of the complementary methodology based on internal standard library, kernel and compiler changes. The positive effect of the instrumentation approach, as will be clear later in this thesis, is that it allows for great precision at the cost of a slightly increased run-time overhead for acquiring traces. This shouldn't be much surprising, given that we are perturbing the baseline performance of the application with additional instructions that serve an analysis purpose, and not the application's business logic goal. Reducing this instrumentation overhead, while affecting the accuracy to the

minimum extent, is a central topic in this thesis which will also be part of more deeper investigations in the future. Another relevant topic is that of controlling the balance between instrumentation accuracy and instrumentation overhead so that different analysis need can be meet. This, however, depends on the particular program being instrumented, the current behavior of the program at run-time and possibly the presence of particular external conditions. Once again, the importance of this topic is recognized in this thesis, but I've only started to to scratch its surface.

The remainder of this thesis is structured as follows. Chapter 2 provides an overview of instrumentation techniques and existing tools. It will then focus on static binary instrumentation and Hijacker, a C toolkit designed to achieve general-purpose static instrumentation through lightweight and non-intrusive injection techniques. Chapter 3 builds on the concepts presented in the previous chapter to give a general perspective on the memory access tracing problem, as well as the most important techniques employed in the literature. Chapter 4 is the heart of this thesis and explains how one can solve the problem of tracing virtual pages by leveraging on finergrained memory tracing techniques. Chapter 5 provides the reader with an experimental and quantitative justification of the goodness of my approach in terms of instrumentation overhead and tracing accuracy. Finally, chapter 6 lays out the conclusions of this thesis and anticipates possible directions for future work.

# $_{ ext{CHAPTER}}$ 2

#### Instrumentation

Your eyes can deceive you. Don't trust them.

— Obi-Wan Kenobi, A New Hope (1977)

Instrumentation is the art and science of measurement and control of the behavior of a program, achieved in such a way as to be transparent to the functioning of the program itself. At its bare minimum, it entails augmenting an application with additional logic and data, while leaving its semantics untouched. Upon running, the program looks and behaves as if it no changes were made to it. Underneath, the actual program behavior has been extended with background functionalities aimed at a variety of different goals. The traditional application of instrumentation techniques is for profiling and monitoring purposes, but other usages are possible. Some interesting uses of instrumentation are to check for programming errors in the code, as well as security breaches. It can also be employed to review the performance of an application, optimize it for future runs and even guide the design of hardware and system components. Generally speaking, instrumentation is a technique that is frequently used to achieved the following goals:

- Profiling the evolution of a program over time in terms of memory access pattern, interaction with the cache subsystem, libraries and the operating system, mostly for optimization purposes, performance modeling and performance prediction.

- Debugging the execution a program to detect unrecoverable errors (e.g. division by zero), security vulnerabilities (e.g. buffer overflows) and correctness violations (e.g. in terms of program state predicates).

- Logging of higher-order application-specific metrics, such as committed vs. aborted transactions in a transactional system, or the number of invalidated events in a discrete event simulation (DES) platform.

• Virtualization and sandboxing, as a way to protect the underlying operating system and run-time environment from malicious code, as well as to decouple the request for software and hardware resources from their actual exploitation.

Instrumentation approaches can be classified at first according to the adoption of either hardware or software tools. As for software instrumentation tools, a natural way to classify instrumentation techniques is: (a) by the software stack level at which they operate—i.e., operating system, environment or application,—(b) by the actual level of abstraction seen by these tools—i.e., source code vs. machine code—and, (c) by the use of either static or dynamic approaches.

#### 2.1 Hardware instrumentation

Hardware instrumentation is characterized at the architectural level by the presence of additional hardware components which are able to perform certain low-level profiling tasks with almost zero-overhead with respect to software-based equivalents [10]. The most common form of hardware instrumentation is high-resolution hot spot analysis and was introduced by the z10 family of IBM processors along with the z/OS proprietary kernel. Finding hot spots in the code allows to understand which portions of the code are run more frequently, so that they can be further optimized for performance purposes.

Interestingly, hardware instrumentation is fully transparent both to the application developer and to the application code. Since all the instrumentation logic occurs in firmware which moves instrumentation data to special-purpose hardware registers, the application code needs no changes. This kind of instrumentation, albeit interesting, is quite rare outside of mainframes and embedded systems. As such, it won't be further investigated.

#### 2.2 Software instrumentation

Software instrumentation approaches are by far the most common. Program patching is performed by injecting additional instructions and data into the original program (or by modifying existing ones) in such a way to implement the desired functionality. This form of patching partially retains the transparency property with respect to the application developer, but requires an additional instrumentation step either at compile-time or run-time (or both). Moreover, it may or may not be transparent to the

application code itself, depending on the specific kind of instrumentation technique being used (i.e., static or dynamic).

A nice property of software instrumentation is that it allows to instrument software located at different logical levels, ranging from the operating system to the final application, including middlewares and libraries. Operating system instrumentation is possible but is rarely employed, as it would require patching a kernel image that follows completely different rules than common executable, but also because it is much easier to extend the system with dynamically-loaded modules. It is by far more common to instrument either the support environment on top of which user-level programs are built, or directly the program themselves. Conceptually, the two choices can be rather similar, it depends on whether the programming language is actually accompanied by an external run-time (as for interpreted languages and just-in-time compiled ones) or relies on traditional compilation techniques. In the latter case, instrumenting the environment means patching one or more libraries which are explicitly invoked by the compiled program.

When talking about patched code, we must specify the level of abstraction spoken by the code itself. To this extent, software instrumentation can occur at three different levels: machine code level, byte code level and source code level.

Machine code level At machine code level, programs are represented by a sequence of instructions and data bytes with no semantics. Instructions are strongly typed in terms of the number of bytes that are involved in an operation. At the same time, data items are seen as a sequence of bytes with no meaning, along with a size. As a result, this layer provides no clues as to how a program is structured, as well as to how data objects in memory must be interpreted. Hence, it is not suitable for high-level instrumentation tasks such as those targeting high-level control flow structures (e.g. try-catch or switch-case statements) or high-level data types (e.g. struct'd or union'd types, classes, callbacks, etc.) On the other hand, carrying out monitoring tasks, such as detecting the memory access pattern of an application, is extremely easy at this level, since all memory operations are explicit. Moreover, this level allows to instrument pretty much every executable resulting from a program written in a compiled programming language, regardless of its syntax and constructs.

Byte code level At byte code level, programs are encoded into an intermediate binary representation which includes a minimal amount of semantic information concerning control flow structures and complex types. This level is provided by interpreters and just-in-time (JIT) compilers for highly abstract languages that aren't directly compiled into machine code. As such,

it is only available in restricted contexts and depending on the programming language in which the application logic is described. The only additional benefit, with respect to the machine code level, is that instrumentation tasks at this level are independent from the architectural idiosyncrasies of the machine. As such, they are transparently compatible with whatever Assembly encoding for instructions is adopted by the hardware.

Source code level At source code level, programs are fully described by extremely complex structures and detailed meta-data. The level of precision that can be achieved at this level in terms of program semantics is the highest of all other levels, and portability of instrumentation tasks is at its finest. On the other hand, injecting instrumentation code within the application is much more complex, since the instrumentation logic must deal complex program statements and data types. At the same time, this kind of instrumentation requires the availability of the original source code file, whose absence makes it impossible to carry out the desired task.

As already anticipated, instrumentation can be a compile-time issue or a run-time one. Techniques that fall to one side or another are respectively called static techniques and dynamic ones.

#### 2.2.1 Static instrumentation

In static instrumentation, changes are applied at the end of the compilation process, thus affecting the execution of the program 'once and for all'. As a result, the instrumentation cost is spent only once, ahead of execution. Observe that static instrumentation is not transparent to the application, since instrumentation code and data are directly inserted into the final executable file being executed. Furthermore, it is not able to fully capture the non-deterministic nature of applications. The program's actual control flow cannot be seen and it can only be modeled through a partially-ordered set of states.

The two main static instrumentation techniques are referred to as relocation and inlining. In *relocation*, the code to be instrumented is duplicated and inserted into a new text segment where it can be freely instrumented. In order for the instrumented code to be run in place of the original one, the original code must be patched with new branching instruction which need to be put at appropriate points in the original code called *instrumentation points*. When an instrumentation point is reached at run-time, the branching instruction diverts the flow to the instrumented region. Then, as soon as the execution of instrumented code completes, another branch diverts the flow back to the original code, until another instrumentation point is met.

This technique is welcomed by researchers because the amount of changes that need to be applied to the original code are minimal. The addresses of non-instrumented code regions need not be changed, therefore references to locations in these regions remain intact. The only requirement is that the instruction which holds the instrumentation point prior to patching the original code be large enough as to accommodate a branch, without overwriting the bytes of a subsequent instruction. This is as simple as it sounds for RISC architecture, but becomes a critical problem in CISC systems. Moreover, the overhead induced by relocation can be measured in terms of two additional branches for each instrumentation point. This can quickly become an issue in modern architectures, since branching instructions can lead to pipeline stalls.

Inlining takes a quite different approach than relocation. Original code is never copied, but rather instrumented in-place by inserting instrumentation code at the desired points, while shifting all instructions that follow. As such, no original instruction in the code is ever replaced—unless the specific instrumentation task to be carried out explicitly asks so. The cost of branching instructions is completely avoided, thus producing a more lightweight instrumentation. On the other hand, all original references to code need to be updated, included those that are indirectly encoded in data sections—e.g., jump tables for switch-case statements and function pointers hold by variables. This task can be more difficult the less meta-data is available in the original executable file to detect or infer with enough confidence the presence of such indirect references.

#### 2.2.2 Dynamic instrumentation

In dynamic instrumentation, also called JIT instrumentation, program execution is patched at run-time, on the basis of the occurrence of particular run-time conditions. This latter approach tends to place a bigger burden on the performance of the instrumented application, since the cost is spent in minimal quantity ahead of execution and heavily at run-time. Also, compared to the static approach, dynamic instrumentation tends to be more opaque to the application developer, since dynamic instrumentation tools usually come in the form of virtual machines (VM) and emulators, that must be explicitly invoked by the user upon launching the client code. However, dynamic instrumentation achieves higher precision than static instrumentation when it comes to tracking the evolution of a program over time, since the control flow is observed on the fly and becomes a streamlined sequence of encountered program states.

The vast majority of dynamic instrumentation toolkits instruments code by either running it natively on the architecture or by means of emulation. In native execution, chunks of the original application are executed on the underlying architecture one at a time. Upon being launched, the instrumentation virtual machine (VM) loads the passed client program into its same address space, intercepts the first instruction of the program and pulls out the first chuck of code, rooted at that instruction. The last instruction of this newly-created chunk is patched so that after the actual execution of that chunk, control is passed back to the VM. The next chunk to be executed is then created, starting from the next instruction which was scheduled for execution prior to patching. During the creation of a chunk, code is instrumented according to the requested rules and external processing functions are possibly invoked for the sake of analysis.

To speed-up execution, a software code cache is maintained where already created chunks are stored. Whenever the VM re-gains control over the application, it first checks whether the next scheduled chunk already exists by looking up in the code cache. In the positive case, the chunk is retrieved and the client program resumes. Another useful technique, named linking, allows to completely bypass the cache look-up mechanism while the current chunk is being created by the VM whenever the next chunk to be executed is already known to be in the cache. In such a case, it is not necessary to invoke the VM dispatcher because the VM itself already knows that the look-up will succeed. For this reason, the last instruction of the current chunk and the first instruction of the next chunk are directly linked.

To ease the task of instrumenting applications in a machine-independent way, some JIT VMs create an intermediate representation (IR) of the code in each chunk where architectural-dependent details are abstracted away in favor of a more explicit and general low-level language (similar in purposes to byte code). This intermediate language features an arbitrary number of virtual registers and explicitly represents the side-effect produced by original machine-code instructions. On the one hand, virtual registers allow to conceal certain register movement operations caused by the high register pressure of the underlying architecture. On the other hand, annotating the side-effect of each instruction makes it possible to the VM to keep track of all the invisible effects that come from its execution. Instrumentation that is performed on the IR is architectural-agnostic and gets implicitly converted into actual machine code at a later stage, when machine-specific optimizations are also performed. Observe that the increased expressiveness inherited from the IR is payed in terms of instrumentation overhead, since the first time a chunk is met the IR must be created, too.

The major drawback of the native execution technique is that it needs to intercept all the instruction that diverts the natural execution flow of the application. These instructions include direct and indirect branches, but even instructions that call privileged services—e.g., through software

interrupts—or generate exceptions. Not only that, but other library and kernel-level 'curlicues' must too be handled. This include asynchronous invocation of callbacks—like the thread-level messaging system of Windows or POSIX's signal handlers—as well as other subtle schemes—such as Pthread's thread creation or the setjump/longjmp library services.

Emulate execution is a technique which is mostly adopted in contexts where security is paramount and client code cannot be trusted. The major difference with respect to the native counterpart is that every machine-level instruction is interpreted, and a virtual processor state is manipulated by the VM which never relinquishes control. The original application therefore is never really executed, but can still be instrumented while its execution is being emulated by the VM. This approach clearly produces an overhead which is degrees of magnitude higher that the other form of execution. Moreover, it becomes quite complex to implement when the ISA that must be emulated is complex too—e.g., x86 and x86-64. Nevertheless, it is more secure than native execution and can provide a sandboxed environment in which the execution of the client program is evaluated without affecting other part of the system.

In my thesis, I will stick to software binary instrumentation techniques, since the kind of task which I wish to carry out—basically, tracing a subset memory accesses—is a natural low-level functionality. As such, it is efficiently performed at machine code level. Moreover, since I want this task to be completed in the most lightweight and less intrusive way—so as not to hamper the performance of the application—static techniques are preferred to dynamic ones.

#### 2.3 Hijacker

Hijacker is the static binary instrumentation tool of choice for my thesis. It has been developed at the *Department of Computer*, *Control and Management Engineering* "Antonio Ruberti" at *Sapienza University of Rome* for high performance computing (HPC) settings [11]. Its main features are the ability to support *general-purpose instrumentation*—i.e., not bound necessarily to profiling or monitoring purposes—and the fact that it poses minimal code overhead on the target applications—a property which is highly desirable in HPC scenarios.

Another peculiar feature of Hijacker is its exclusive support for relocatable files, as opposed to executable ones. The main difference between relocatable files and executable ones is that executable files can be directly loaded into a process' address space, while relocatable files are typically not amenable to loading and must pass through an additional linking step. More precisely, an executable file is the union of one or more relocatable files, as

performed by the static linker during the compilation process. Hence, the main advantage gained from instrumenting a relocatable file is that it allows an instrumentation tool not to take care of any complex linking logic. Once again, this is the approach taken by Hijacker. A pictorial representation of the instrumentation process performed by Hijacker on relocatable files is shown in figure 2.1.

Figure 2.1: Hijacker's instrumentation process

In relocatable object files, the program is seen as a sequence of sections, each of which contains a different kind of information. Some sections contain program code, some program data. Other sections are only needed to guide the linking process and won't make through this step. All references to objects and places within each section are expressed as displacements from the beginning of the section and sometimes accompanied by detailed annotations called relocations. Therefore, relocatable objects never refer to functions or variables through virtual addresses, but rather through displacements and relocations. When the linked is fed with a relocatable object, it consumes all relocations and converts the relative addresses represented by displacements into absolute addresses, which are directly mapped into the virtual memory as virtual addresses. Those sections that were only needed for linking are discarded and the remaining ones become segments which are amenable to being loaded into virtual memory at program launch.

As with other compiling and instrumentation tools, Hijacker relies on the notion of intermediate representation. In some compilers, such as the LLVM compiling suite [12], a program source code is translated into an intermediate low-level representation that flattens complex control and data structures into simpler equivalents, as machine code does, while retaining the property of being machine-independent. Because of this, every optimization and manipulation that can be performed on a client program is done at the intermediate level, and translation to the final machine code is only performed as the last compilation stage. In Hijacker, the intermediate representation has similar but not exactly equivalent purposes. In fact, it is a representation for relocatable files rather than for source code, meaning that it creates an abstract representation of relocatable files in terms of sections, relocations and other entities.

The internal software architecture of Hijacker is depicted in figure 2.2. From an extremely high-level perspective, Hijacker is the combination of a front-end module and a back-end one. The *front-end* is responsible for parsing an input relocatable file and emitting another relocatable file which results from instrumenting the former. The *back-end* module takes care of the actual instrumentation tasks and is responsible for maintaining and altering the intermediate binary representation (IBR).

FIGURE 2.2: Hijacker's software architecture

#### 2.3.1 Front-end

The front-end is the first and last module to take control of the entire instrumentation procedure. It is divided into three additional components:

• The *file loader* parses the input relocatable file and creates an internal mapping of sections, relocations and other entities (e.g. functions and instructions) where displacements from the beginning of sections are replaced by memory pointers. Eventually, the result of this operation is the IBR that will be the subject of all manipulation throughout the entire instrumentation process.

- The *rule parser* takes as input an XML file containing the requested instrumentation rules to apply to the relocatable file. It is specified by the user and its existence represents the support for general-purpose instrumentation tasks. Specifically, rules are registered and fed to an back-end subcomponent which is in charge of executing them in sequence.

- The *file writer* has the opposite role of the first. It converts the modified IBR into the same binary encoding that were used to describe the original relocatable file. As such, memory pointers are converted again into (updated) displacements from the beginning of sections and the IBR is eventually discarded.

The file loader and the file writer, during their execution, interact with two interpreters that operate at two different representation levels. The executable interpreter is the one which is directly responsible for building up the IBR for the relocatable file. When faced with instructions belonging to the code of the program, it gives controls to the code interpreter. The latter converts the machine-code instructions into an abstract representation which encodes the entire program logic as a chain of instruction descriptors. This representation is eventually fed back to the executable interpreter, which derives descriptors for functions and ultimates the IBR. In the inverse direction, the one needed by the file writer, functions and instructions in the IBR are converted back to their binary encodings.

It is worth saying that both the executable interpreter and the code interpreter are designed in such a way to support respectively multiple *object file formats* (OFFs) and multiple *instruction set architectures* (ISAs). Currently, Hijacker only supports ELF relocatable file formats and IA32/AMD64 machine-level encoding, although support for additional formats and instruction sets is on its way.

#### 2.3.2 IBR

The Intermediate Binary Representation (IBR) provided by Hijacker can be seen as a pointer-based representation of the same contents included in the input relocatable file and referenced through displacements. Observe that manipulating memory pointers is much easier than manipulating displacements. For example, inserting a new instruction only requires to change the memory pointers of the pivot instruction and update those of the newly inserted one. Hence, changes are local and don't disrupt the value of other pointers. On the contrary, if the same insertion were performed directly on the relocatable input file, it would require to shift the displacements of all instructions that follow the newly inserted one, thus causing global changes.

FIGURE 2.3: Hijacker's internal binary representation

The internal composition of the IBR takes much of its inspiration from ELF relocatable files. As such, every other supported object format will be converted into a representation that is highly inspired from ELF. In this representation, we find three different components: sections, symbols and relocations. Two additional types, functions and instructions, are built for convenience and find no direct equivalent in any relocatable OFF. They are required to provide Hijacker with a basic abstract representation of program code. A visual description of Hijacker's IBR is provided in figure 2.3.

#### Section

Sections represents coarse-grained portions of a relocatable file. Unavoidable ones are those for program code and program data. Other ones are self-referential and contain, for instance, symbols or relocations. As already explained, some of the sections that make up the file will eventually become segments which can be loaded in memory when a process is created. All sections that hold a portion of the compiled program in terms of code and data belong to that category. Other sections, such as those which are self-referential, are consumed by the static linker upon linking while producing the final executable for the program.

#### Symbol

In ELF and other OFFs, symbols represent finer-grained byte sequences than sections associated with a name, a size and a meaning in terms of linking logic. They are the main target of relocations and can represent data object, functions, relocatable sections and other entities. Symbols are contained into a special section named symbol table. Inside the symbol table, each entry is a different symbol. Beside the symbol name, size and other flags, a symbol's entry also tells the linker the section and displacement within that section in which the symbol will be located inside the final executable file. This is true for data symbols representing object such as array and variables in general.

#### Relocation

Relocations are the peculiar feature of relocatable files. A relocation is an entry in a special-purpose relocatable section which describes that a reference to a given symbol is performed at a given point in the program (e.g., in the program code). Stated differently, a relocation represents the fact that at a given displacement from a section, a reference to a certain location displaced from the beginning of a symbol occurs. The most common forms of relocations are references to C variables—triggered by memory movement operations,—functions—triggered by call instructions—and instructions—triggered from jump tables in data sections to encode the addresses of case statements, but also the addresses of functions in the presence of indirect branch instructions.

Relocations are a convenient form of annotation for memory references whenever virtual addresses aren't available. Since references to symbols are expressed through rich meta-data, the exact location of such symbol in terms of its virtual addresses is not needed. By the time the linker concludes its job, all relocations have been consumed and flattened into real hard-wired virtual memory addresses which explicitly refer locations in the executable where symbols reside.

#### Instruction and functions

Instructions in Hijacker are represented with high-level descriptors that simply encode the size and type of the instruction (e.g. memory read, memory write, integer, floating point, logical), its displacement from the beginning of the code section, the presence of a relocation to a data symbol (if any), and other architectural details. Moreover, instruction descriptors are linked into a bi-directional chain that makes the implementation of many low-level instrumentation tasks such as instruction insertion or deletion much easier. Functions are derived from the instruction chain by checking the original displacements of instructions against the displacements of the respective function symbols. Eventually, a list of function is created where each function records mainly its name and first instruction.

#### 2.3.3 Back-end

The back-end represents the core of the instrumentation facility. It is composed mainly of the *rule engine*, which is responsible for executing the previously stored rules on the current IBR. Many different rule types are supported. Among them, we can mention those that add new instructions to the representation or those that replace existing ones. Furthermore, Hijacker allows to easily inject new code into the program (either written in Assembly or C technology), as well as to transparently call user-defined function at desired point so as to execute the actual desired functionality (be it monitoring, profiling, debugging or whatnot form of logic). Finally, the *instrumentation engine* is invoked by the rule engine to actually manipulate the IBR. It is composed of many manipulation functions for section, symbol, relocation, function and instruction descriptors.

#### 2.4 State of the art

In the rest of this chapter, an evaluation of some of the most popular instrumentation frameworks is provided. Later in this section, such frameworks are compared against each other and with the Hijacker toolkit. Hopefully, this should put into perspective the kind of instrumentation that I wish to achieve for my thesis, in terms of its strengths and limitations.

#### 2.4.1 PEBIL

PEBIL (PMaC's Efficient Binary Instrumentation Toolkit for Linux) is a static binary instrumentation tool for Linux x86 and x86-64 which uses relocation as its main technique [13]. Not only that, but it is heavily oriented toward lightweight and general-purpose instrumentation, just like Hijacker. The high-level functioning of PEBIL is as follows. Whenever an instrumentation point is encountered while scanning the application's code, PEBIL injects a branch instruction that gives control to an instrumentation preamble. This instrumentation code saves the program state, invokes a user-defined function that performs the requested tasks, restores the previously-saved state and then branches back to the instrumentation point.

To provide sufficient space for the insertion of branches, PEBIL relocates code at the function-level so that before any possible instrumentation point a branch instruction can be injected. This procedure is split into four different steps. In the first step, the contents of original functions are relocated into an area of the code section that is allocated by PEBIL and private to it. Relocating the contents of function is an elegant way to leave function entry point unaltered. To link the entry point of the original instruction to

the actual relocated contents, the original entry point is replaced with an unconditional branch to the relocated function.

The motivation behind function-level relocation is that typical text segments in a final executable are such that the next instruction after the end of a function is the entry point for another function. This is to say that function code is not aligned nor padded, hence inserting additional instructions in the code would require shifting all those that come after the insertion point, included the entry points to other functions. This procedure is particularly delicate when it comes to executable files, as relocation entries are gone. Therefore, references to other instructions and data object must be recognized and update while shifting the instructions. Shifting is further complicated by the fact that indirect call instructions may be present in the code, which are hard to resolve before run-time. If PEBIL changed the entry points to functions, it would have to tentatively discover indirect calls, trace back call tables in data segments and update entry point addresses accordingly. Quite a complex and unreliable task.

The second step deals with padding instructions in the relocated code. For each instruction, an empty space is inserted before it and filled with a sufficient number of null instructions as to accommodate the potential insertion of a branch. On x86 and x86-64, 5 bytes are sufficient to hold a jump instruction to a near code location. Whenever a regular instruction is already a branch then it is 'self-padded', meaning that the byte length of a branch instruction taking less than 5 bytes is increase up to this size. Observe that this task would not be needed if the ISA of reference were that of a CISC architecture, since in that case all instructions would take up the same byte length. However, the cost of supporting a quite widespread family of processors such as x86-(64) is paid exactly by its intrinsic ISA complexity.

The third step is the actual instrumentation. If a regular instruction in the relocated code is recognized as an instrumentation point, a branch instruction is inserted before it—or in place of it when it comes to existing branch instructions. By executing the newly inserted branch, control is passed to PEBIL's instrumentation preamble. As already explained, this preambles saves the current architectural context and then invokes an analysis procedure which is defined by the user in a high-level language such as C. After returning from the analysis procedure, the architectural stare is restored and the application execution is resumed.

The major overhead of PEBIL's instrumentation at run-time comes from the insertion of additional branches in the code to achieve function-level relocation and invoke the analysis routine, resulting in possible control hazard at the micro-architectural code level. Moreover, as explained by the authors, "since the code is being reorganized and expanded, some positive alignment and size optimizations that the compiler might have made on the instructions in the function might be destroyed." Nevertheless, the effects of relocating code and padding instructions alone, that is without branching to PEBIL's instrumentation code, are measured on the SPEC CPU2000 Integer benchmark to be no higher than 5% more of the non-instrumented execution.

Another critical source of overhead comes from the analysis procedure itself, whose execution can pollute instruction and data caches to an arbitrary extent. Not only that, but it also requires PEBIL to save and restore the processor context, which is a very expensive operation. Notice that beside functions written in a higher-level language, PEBIL also enables the insertion of lightweight assembly-level instrumentation snippets. Code snippets written in low-level language minimize the effects of cache pollution and relieve PEBIL from the save/restore logic. The task of preserving the value of registers is now in charge of the snippet itself, which can optimize it by only saving and restoring those registers that will be actually employed.

An experimental evaluation of PEBIL's performance is derived, again, from running an instrumented version of the SPEC CPU2000 benchmarks. The analysis function in this experiment is in charge of counting the number of times that a basic block is executed. Basic blocks are explained to a deeper extent in chapter 4. Basically, they are contiguous sequence of instructions where either the first instruction is the target of a jump, or the last instruction is a jump operation itself. Counting the number of times a basic block is executed allows to estimate the overhead introduced by PEBIL while minimizing that introduced by the analysis code, which can be implemented as an Assembly snippet. As can see from picture 2.4, the average overhead measured for PEBIL is 62%, compared to 151% for Pin, 408% for DynamoRIO and 734% for Valgrind.

#### 2.4.2 DynamoRIO

DynamoRIO is defined by its authors as a dynamic optimization infrastructure for the IA32 family of architectures and the Windows environment [14]. The main idea behind this tool is to optimize the execution of a program while it is running, thus overcoming the obstacles that are traditionally posed by static compilation. Compilers are in fact incapable of predicting the behavior of applications at run-time, therefore the kind of optimizations that can be performed on program is restricted to those enabled by static analysis. The main obstacle to dynamic optimization is that of maintaining control over the running application at frequents points in its execution. In practice, this means intercepting instructions that divert the regular execution flow of the application—for instance, branch instructions—as well as instruction that perform a more aggressive form of control flow hijacking—

FIGURE 2.4: Performance evaluation of PEBIL with respect to other instrumentation tools.

such as those raising exceptions or invoking privileged services.

Conceptually speaking, DynamoRIO is a JIT optimizer which acts as a wrapper around the actual executable. Code from the original program is executed natively in blocks of consecutive code called *fragments*, which terminate as soon as a control flow instruction is met. Such instruction is intercepted so as to give control back to the DynamoRIO VM. Fragments persist in a software-defined code cache for fast retrieval and are linked together to avoid returning to DynamoRIO's code at boundaries whenever possible. Among them, those that have been identified as being executed more frequently can be optimized by the VM to improve the performance of the running application. Observe that beside direct and indirect branches, Windows supports several other abnormal ways to transfer flow from one point in the program to another. For instance, Windows supports callback mechanisms for thread-level message queues. Another form of control flow hijacking is exceptional control flow. All such mechanisms are successfully intercepted by DynamoRIO.

To evaluate the slowdown incurred by applications run through DynamoRIO, the SPEC2000 suite of benchmarks is executed without any form of dynamic optimization. The results of this experiments in picture 2.5 show that apart from pathological cases the slowdown introduced by DynamoRIO is never higher than 2.0x.

FIGURE 2.5: Performance evaluation of DynamoRIO with no dynamic optimization.

#### 2.4.3 Pin

Pin is a dynamic instrumentation framework available for Linux platforms for IA32, AMD64, IA64 and ARM architectures [15]. Its design goals are usability, transparency, portability, efficiency and robustness. The first three goals are achieved thanks to a flexible API to develop Pin plug-ins, called *Pintools*, which allows users to instrument arbitrary code locations. Many of the tasks needed to preserve the correctness of the application—such as saving and restoring the processor state—are handled in a transparent manner by Pin, which also abstracts away all the architectural-specific issues that must be handled. Efficiency is achieved by improving JIT instrumentation through code caching, trace linking, inlining of analysis functions and register re-allocation. Another important source of efficiency is given by the Pin's ability to attach and detach from a running process, so as to activate and deactivate instrumentation. Lastly, the robustness of Pin comes from the fact that by using dynamic instrumentation many classic issues of static approaches—such as not knowing the actual targets of indirect branch targets or not being able to instrument external libraries are—are naturally absent.

The main technique adopted by Pin to instrument code is JIT native execution. Pin receives the original executable as an input, intercepts the first instruction and decompiles a contiguous sequence of instructions, named trace, which ends with a branch instruction. Once a trace has been identified, Pin re-compiles it in such a way as to (a) instrument it according to the desired rules and (b) make sure that the last instruction of the block gives control back to Pin's code. Then, Pin executes this re-compiled block natively on the architecture. It must be noted that for efficiency purposes, all code which passes through Pin is transformed from one ISA directly into the same ISA without passing through an intermediate format. After regaining

control, Pin repeats the same step for a trace rooted at the original branch target. A software code cache is maintained to store previously-recompiled traces so as no to incur again in the recompilation overhead.

Pin also supports trace linking, in an attempt to directly move from one trace to another whenever the destination trace is already in the code cache. This avoids the expensive passage from the application code to Pin and from Pin back into the application code. Another useful performance booster is the inlining of analysis functions inside the code to be instrumented, similarly to what PEBIL does. Without inlining, control must first pass to a bridge routine which protects the current architectural state prior to calling the analysis snippet. In total, instrumenting code through the bridge routine requires two calls and two returns. With inlining, on the contrary, the bridge routine is avoided and the analysis snippet is directly inserted into the application code, thus sparing the previous instrumentation cost in its entirety. A register allocator is in charge of handling possible register conflicts that occur in the analysis routine, by exploiting possible dead registers or temporary spilling out-of-context application registers to the stack.

Experimental results on the SPEC2000 test suite indicate that the speed-up gained from running Pin without any optimization to running it with all optimization enabled can be as large as 10x on some benchmarks, as seen in 2.6. A comparison of Pin, DynamoRio and Valgrind on the basic block counting experiment suggests that Pin is 2x faster than DynamoRio and 3x faster than Valgrind. On the other hand, when instrumentation is disabled to appreciate the intrinsic overhead introduced by these tools at run-time, Pin is considerably faster than Valgrind, but slightly less performing than DynamoRIO. This is likely due to the fact that while DynamoRIO is thought as a framework to optimize the execution of applications, Pin optimizations are thought for instrumentation purposes.

FIGURE 2.6: Performance evaluation of Pin alone with and without optimizations.

#### 2.4.4 Dyninst

Dyninst is a binary instrumentation tool which puts strong emphasis on the flexibility goal [16]. It can instrument a binary file either by using static instrumentation techniques or by relying to dynamic approaches (a technique called anytime instrumentation). Moreover, it can instrument executables at any level of abstraction (anywhere instrumentation), ranging from instruction-level to function-level, including basic blocks in the control-flow graph (for an explanation of these two concepts, see chapter 4). The authors of Dyninst claim that it able to produce an instrumentation overhead which is always proportional to the number of instrumented locations, independently on the kind of instrumentation being used.

The basic idea for anywhere instrumentation is to allow user-defined analysis functions to manipulate program code by providing different kind of instrumentation points. Typical instrumentation tool, included Hijacker, only allows an external function to gain control over an instrumented application prior to or immediately after the execution of a particular kind of instruction (e.g., memory read, memory write, floating point, etc.) Dyninst, on the contrary, provides additional instrumentation points such as function entry/exit, basic block entry/exit, loop entry/exit and loop iteration entry/exit. These additional points are supported through the manipulation of a global CFG whose nodes and edges are appropriately tagged. A peculiarity of Dyninst is that instrumentation code is directly inserted in this global CFG by means of additional nodes and edges. The augmented CFG which results from the instrumentation is later used to generate the final instrumented binary code.

To achieve proportional instrumentation cost, Dyninst chooses the code that must be relocated and patched, then creates a relocated copy for the selected code and instruments it with the desired rules. Finally, it patches the original code so that control will be diverted to the relocated region. To achieve anytime instrumentation, two techniques are introduced. The first, called state interception, allows to move to the relocated region while running the original code version. Rather than patching the original code, state interception overwrites the process context by altering the content of the program counter, so that control is transparently passed to the instrumented version. The second technique, named iterative instrumentation, allows users to augment previously instrumented code with further instrumentation, or to remove pre-existent instrumentation so as to switch back to normal execution. It internally employs state interception to move back and forth between instrumentation versions, but it also allows to achieve overhead proportionality since non-instrumented code can always be executed.

To evaluate the performance of Dyninst, the SPEC2006 benchmark was

instrumented with a simple basic block counting logic. The obtained results suggest that the overhead incurred by Dyninst is competitive with that of Pin, DynamoRIO and PEBIL on almost all benchmarks. Moreover, Dyninst achieves considerably less overhead than Pin when it comes to measuring the proportionality metric, as shown in 2.7. This results from the fact that Pin unconditionally intercepts all the executed code, included non-instrumented one.

FIGURE 2.7: Evaluation of the proportionality metric for Pin, PEBIL and Dyninst.

#### 2.4.5 Valgrind

The main purpose of Valgrind is to enable extremely flexible and powerful dynamic instrumentation which, although heavyweight, allows to carry out complex analysis task which would not be feasible with other instrumentation tools [17]. The flagship of Valgrind, as opposed to other tools, is the support for shadow values. A shadow value is an in-memory annotation that describes the value of one register of memory location used by the program with another value. The meaning of a shadow value is defined contextually to the kind of analysis one wishes to perform. Apart from that, the execution of a program is always reflected by a shadow execution which operates on shadow values.

Many popular plug-ins have been implemented on top of Valgrind's core and its support for shadow values. The most popular tool, Memcheck, uses shadow values to keep track of which bit values are uninitialized and can report accesses to undefined memory area with extremely high precision [18]. Other useful tools have been developed, but overall they account for less than 20% of Valgrind use by programmers. Another reason for running applications against a Valgrind tool is that Valgrind has its own memory allocator that is able to intercepts calls to malloc and free operations. This allows Valgrind tools such as Memcheck to even notify the user about incorrect usage of the heap, which is mostly due to memory leaks.

Similar to other dynamic instrumentation frameworks, Valgrind uses dynamic binary re-compilation. Whenever a program is run in Valgrind, it is

loaded into the same address space as the invoked Valgrind tool. Application code is disassembled and re-compiled one code block at a time. The disassembly product is an IR which is the target of the instrumentation tasks carried out by the currently executing Valgrind tool. After instrumentation, the result of is stored in a core cache so that the same code block doesn't have to go through the same process again in the future. Whenever the execution of a translated block completes, the application relinquishes control and gives it back to the Valgrind dispatcher, which checks whether the next block to execute is already present in the code cache and, if not, creates it. Contrarily to other dynamic instrumentation tool, direct chaining of code blocks is not supported.

In the IR, the actual registers used by the host machine (hence called host registers) are replaced with a set of guest registers to abstract away the architectural limitations of having high register pressure and frequent register spilling. Furthermore, a single architectural instruction might be replaced by multiple IR instructions that describe, beside the visible effect of the real instruction, all its side-effects. This IR is convenient to manipulate for Valgrind tools because it is architecture-independent and highly expressive.

To translate a single code block into an instrumented block, the process is as follows. First, a code block is recognized according to some criteria (e.g., by parsing instructions until a conditional branch is met). Then, each instruction is disassembled into its IR code, which operates on guest registers. The resulting IR is optimized by removing redundant and unnecessary operations, as well as performing constant folding, common subexpression elimination and other kinds of flattening analysis. Then, the Valgrind tool instruments the code block according to its own policy. Eventually, the IR is translated back into machine-dependent code by first replacing guest registers with host registers and then converting each IR expression into a valid machine-level instruction.

The experiments conducted on the SPEC2000 benchmarks to evaluate the baseline overhead induced by Valgrind yield results which are consistent with the findings of other researchers. Valgrind is 4x slower than Pin and 4.4x slower than DynamoRIO when no instrumentation is performed. Similarly, when basic block counting is evaluated, the slowdown with respect to Pin and DynamoRIO are respectively 3.3x and 2.0x. However, the purpose of Valgrind is to enable heavyweight complex instrumentation, rather than lightweight instrumentation tasks. For this reason, the observed slowdown as compared to other instrumentation tools is actually expected and quite acceptable in perspective.

#### 2.4.6 Comparison

This section is devoted to comparing the previously-discussed frameworks according to the following criteria. First of all, tools can employ either static or binary instrumentation. The benefits and drawbacks coming from the employment of one technique over another have been discussed in section 2.2. Second, they can work at different stages in the compilation process, with the differences being highlighted in section 2.3. Another interesting classification is the level of granularity at which instrumentation can occur (e.g., function-level, instruction-level, etc.) which is reflected in the overall flexibility of the instrumentation toolkit.

Beside the usage of static or dynamic approaches, an instrumentation framework is also identified by the specific techniques that are put into practice (e.g., relocation or native IR-aided JIT instrumentation). Among them, we stress multi-versioning, which in principle can be employed to switch at run-time between differently instrumented version of the same executable (including the baseline non-instrumented version) so as to place different degrees of overhead over the instrumented application. This can be useful in certain scenarios (e.g. transactional processing systems) where the workload to which an application is subject can change over time as a function of external input or system events.