### SAPIENZA UNIVERSITY OF ROME

Ph.D. Program in Computer Engineering

XXV Cycle - 2012/3

Design of Software Support Structures for High Performance Optimistic Simulations with Special Focus on Multi-Core Hosting Environment

Roberto Vitali

### SAPIENZA UNIVERSITY OF ROME

#### Ph.D. Program in Computer Engineering

XXV CYCLE - 2012/3

### Roberto Vitali

## Design of Software Support Structures for High Performance Optimistic Simulations with Special Focus on Multi-Core Hosting Environment

Thesis Committee

Reviewers

Prof. Francesco Quaglia (Advisor)

Prof. Leonardo Querzoni

Prof. Christopher D. Carothers

Prof. George F. Riley

AUTHOR'S ADDRESS:

Roberto Vitali

Dipartimento di Ingegneria Informatica, Automatica e Gestionale Sapienza Università di Roma

Via Ariosto 25, 00185 Roma, Italy

e-mail: vitali@dis.uniroma1.it

www: http://www.dis.uniroma1.it/~vitali/

# Contents

| 1 | Inti | roduct  | ion                                                  | 5  |

|---|------|---------|------------------------------------------------------|----|

|   | 1.1  | Parall  | lel Discrete Event Simulation                        | 5  |

|   | 1.2  | Optin   | nistic Synchronization Overview                      | 8  |

|   | 1.3  | Thesis  | s Contributions                                      | 12 |

| 2 | Lite | erature | e Survey                                             | 15 |

|   | 2.1  | State   | Recoverability                                       | 15 |

|   | 2.2  | Memo    | ory Management                                       | 18 |

|   | 2.3  | Balan   | ced and Fruitful Usage of Resources                  | 21 |

| 3 | Ref  | erence  | e Environment                                        | 25 |

|   | 3.1  | Hardy   | ware and Base Software                               | 25 |

|   | 3.2  | The F   | ROOT-Sim Platform                                    | 27 |

|   |      | 3.2.1   | Exposed API                                          | 29 |

|   |      | 3.2.2   | Code Examples                                        | 30 |

|   |      | 3.2.3   | ROOT-Sim audience                                    | 32 |

|   | 3.3  | Bench   | nmark Applications                                   | 32 |

|   |      | 3.3.1   | Personal Communication System                        | 32 |

|   |      | 3.3.2   | Traffic                                              | 34 |

| 4 | Aut  | tonomi  | m ic~Log/Restore                                     | 37 |

|   | 4.1  |         | istence of Different Log/Restore Modes               | 37 |

|   |      | 4.1.1   | Starting from Non-Incremental State Saving Supports: |    |

|   |      |         | DyMeLor Details                                      | 37 |

|   |      | 4.1.2   | Incremental State Saving Supports                    | 38 |

|   |      | 4.1.3   | State Log Operations                                 | 43 |

|   |      | 4.1.4   | State Restore Operations                             | 44 |

|   |      | 4.1.5   | Caching Write References for Latency Reduction while |    |

|   |      |         | Managing the Memory Map                              | 45 |

|   |      | 4.1.6   | Interaction with Third Party Libraries               | 46 |

|   |      | 4.1.7   | The Dual-Coding Scheme                               | 46 |

|                  | 4.2   | Log/Restore Overhead Modeling                | 48  |

|------------------|-------|----------------------------------------------|-----|

|                  | 4.3   | Autonomic Optimization                       | 50  |

|                  | 4.4   | 4.3.1 Run-time Parameter Sampling            | 53  |

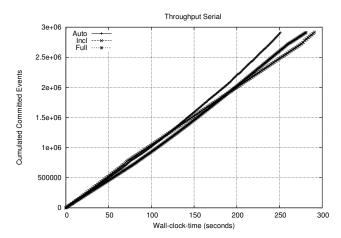

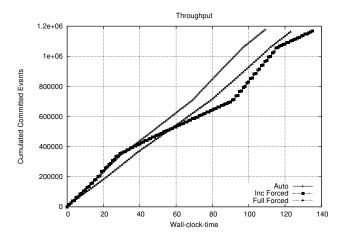

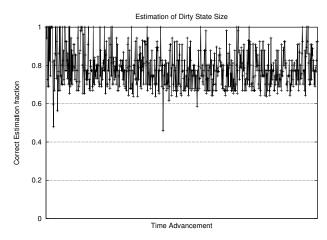

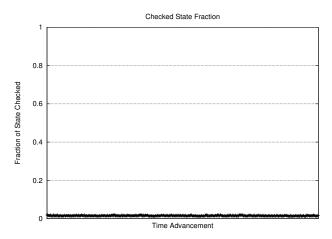

|                  | 4.4   | Experimental Results                         | 57  |

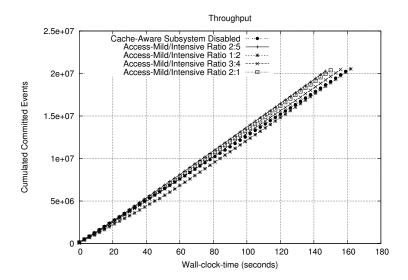

| 5                | Cac   | che Aware Memory Delivery Mechanisms         | 63  |

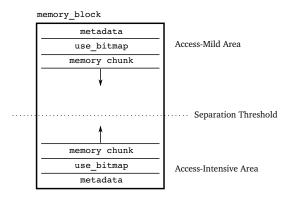

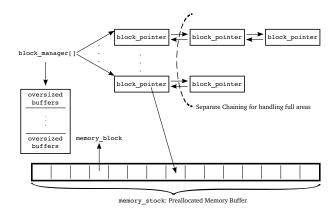

|                  | 5.1   | Cache-Aware Memory Manager Design            | 64  |

|                  |       | 5.1.1 Rationale                              | 64  |

|                  |       | 5.1.2 Design Details                         | 65  |

|                  | 5.2   | Details on Actual ROOT-Sim Integration       | 66  |

|                  | 5.3   | Experimental Results                         | 71  |

|                  |       | 5.3.1 Benchmark Parametrization              | 71  |

| 6                | Loa   | d-Sharing on Multi-Core Machines             | 75  |

|                  | 6.1   | Base Discussion                              | 75  |

|                  | 6.2   | The Load-sharing Model                       | 78  |

|                  |       | 6.2.1 Asymptotic Costs Analysis              | 81  |

|                  | 6.3   | Architectural Aspects                        | 82  |

|                  |       | 6.3.1 Details on Actual ROOT-Sim Integration | 86  |

|                  | 6.4   | Overhead Oriented Experimental Assessment    | 87  |

|                  |       | 6.4.1 Overview of the Assessment             | 87  |

|                  |       | 6.4.2 Benchmark Application Setting          | 91  |

|                  |       | 6.4.3 Results                                | 91  |

|                  | 6.5   | Evaluating the Effectiveness of Load-Sharing | 101 |

| 7                | Cor   | nclusion                                     | 107 |

|                  |       |                                              |     |

| $\mathbf{B}^{i}$ | iblio | graphy                                       | 113 |

# Abstract

Parallel Discrete Event Simulation (PDES) is a classical means to achieve high performance simulations. This is especially important on contexts entailing real-time constraints, as for the case of decision making tools, where target configurations have to be identified, via simulation, within bounded time. PDES is based on splitting the model to simulate in different simulation objects, that are mapped onto logical processes (LPs), which can process simulation events in parallel, thus potentially allowing for (large) speedups when compared to traditional serial execution of the simulation model. On the other hand, synchronization mechanisms need to be actuated in order to allow the parallel run to provide correct results, hence correct evolution of the objects' state along the simulation time axis.

In this dissertation we cope with performance of PDES systems, with special focus on deploys of the PDES platform onto multi-core architectures. These architectures represent the current CPU trend and nowadays it is common to have chips with a significant number of cores, sometimes enough for effectively performing parallel computations within a single chip. By design, these architectures share most of the CPU internal components across different cores, and physical memory across the different CPUs. This implies several drawbacks, mainly due to the contention, but at the same time, such a sharing can become a resource, if well exploited through sector specific software design.

The base building block for our work is the optimistic PDES synchronization paradigm, which has been shown to be highly promising in terms of potential for fruitful parallelism exploitation.

As a first contribution, we will present the design and implementation of optimized supports for state log/restore operations, which are at the base of the rollback procedures used to guarantee consistency in the optimistic paradigm. System requirements for these supports only entail the x86 instruction set, with no particular additional facilities to be offered by the underlying computing platform. On the other hand, the provided solution has a further reflection on performance for deploys on multi-core systems since it aims at

automatizing the optimization of a set of CPU/memory tradeoffs among which we also find virtual memory usage, which may impact physical memory (e.g. cache) contention for the case of multi-core architectures.

Secondly, we address the issue of optimizing the behavior of the caching hierarchy by providing an innovative buffer delivery mechanism suited for memory demands in optimistic PDES systems. This is a quite relevant aspect to cope with, given the intrinsic high-demand of virtual memory by optimistic PDES runs. The proposed solution tends to reduce the impact of virtual memory demand on physical memory, which is achieved in a highly general manner, thus making the approach applicable to differentiated types of hardware architectures. However, by nature, it reveals particularly suited for the case of multi-core systems, given the aforementioned issue if physical memory contention across the cores.

Finally, we provide an additional contribution, specifically tailored to the multi-core architecture, which introduces an innovative load-sharing paradigm for optimistic PDES platforms. It is aimed at improving performance and fruitful resource usage in a fully orthogonal manner with respect to traditional load-balancing. In fact, it allows the computing resources to be (dynamically) assigned to each simulation platform instance on the basis of its current workload, instead of migrating the workload from one kernel to another. This also has the advantage of not suffering from all the issues related to workload (namely LPs) remapping (i.e. data and metadata migration), leading to the simplification of the job of both application programmers and simulation-system developers.

To assess the real benefits, all the above approaches have been implemented within ROOT-Sim, an open source C-based Optimistic Simulation platform targeting the optimistic synchronization paradigm, and several experimental studies have been conducted, whose outcomes are reported in the thesis.

### Chapter Organization

This dissertation is structured as follows. The first chapter provides details on the PDES approach, with the special focus on the optimistic synchronization paradigm. It also provides hints on multi-core architectures, which have been used as the reference hardware environment for this study. In chapter two, state of the art results in the context of PDES systems, which are more or less related to the presented approaches, are discussed. The third chapter provides an overview of both hardware and software environments exploited to ultimately assess the effectiveness of our proposals. Original contributions by this dissertation start form chapter four, where an Autonomic State Saving architecture is designed, implemented and tested. Chapter five introduces

our innovative memory delivery mechanism, explicitly targeted at optimistic PDES systems, and reports experimental data demonstrating its viability and advantages. Chapter six presents the load-sharing approach/model, which explicitly targets multi-core environment, its implementation and profiling/performance data showing its dynamics and effectiveness. Finally, chapter seven concludes the dissertation by summarizing the provided contributions.

Most of the material provided by this dissertation has been presented in (or has contributed to the production of) the following technical articles I have coauthored:

- 1 Roberto Vitali, Alessandro Pellegrini, and Francesco Quaglia. Load sharing for optimistic parallel simulations on multi-core machines. *ACM Performance Evaluation Review.* vol.4, no.3, 2012.

- 2 Roberto Vitali, Alessandro Pellegrini, and Francesco Quaglia. Autonomic state management for optimistic simulation platforms. In Preparation for submission to an international journal.

- 3 Roberto Vitali, Alessandro Pellegrini, and Francesco Quaglia. A load sharing architecture for optimistic simulations on multi-core machines. In *Proceedings of the 19th International Conference on High Performance Computing*, HiPC. IEEE Computer Society, December 2012.

- 4 Roberto Vitali, Alessandro Pellegrini, and Francesco Quaglia. Assessing load sharing within optimistic simulation platforms (invited paper). In *Proceedings of the 2012 Winter Simulation Conference*, WSC. Society for Computer Simulation, December 2012.

- 5 Roberto Vitali, Alessandro Pellegrini, and Francesco Quaglia. Towards symmetric multi-threaded optimistic simulation kernels. In *Proceedings of the 26th International Workshop on Principles of Advanced and Distributed Simulation*, PADS, pages 211–220. IEEE Computer Society, August 2012.

- 6 Roberto Vitali, Alessandro Pellegrini, and Gionata Cerasuolo. Cacheaware memory manager for optimistic simulations. In *Proceedings of the 5th International ICST Conference of Simulation Tools and Techniques*, SIMUTools, March 2012. Winner of the Best Paper Award.

- 7 Alessandro Pellegrini, Roberto Vitali, and Francesco Quaglia. The ROme OpTimistic Simulator: Core internals and programming model. In Proceedings of the 4th International ICST Conference on Simulation Tools and Techniques, SIMUTools. ICST, 2011.

- 8 Roberto Vitali, Alessandro Pellegrini, and Francesco Quaglia. Autonomic log/restore for advanced optimistic simulation systems. In *Proceedings of the Symposium on Modeling, Analysis, and Simulation of Computer and Telecommunication Systems*, MASCOTS, pages 319–327. IEEE Computer Society, 2010.

- 9 Roberto Vitali, Alessandro Pellegrini, and Francesco Quaglia. Benchmarking memory management capabilities within root-sim. In *Proceedings of the 13th IEEE/ACM International Symposium on Distributed Simulation and Real Time Applications*. IEEE Computer Society, 2009.

- 10 Alessandro Pellegrini, Roberto Vitali, and Francesco Quaglia. Di-DyMeLoR: Logging only dirty chunks for efficient management of dynamic memory based optimistic simulation objects. In *Proceedings of* the 2009 ACM/IEEE/SCS 23rd Workshop on Principles of Advanced and Distributed Simulation, PADS, pages 45–53. IEEE Computer Society, 2009. Candidate for (but not winner of) the Best Paper Award.

# Chapter 1

# Introduction

Simulation is an attractive and well consolidated methodology to study real world phenomena. It has been exploited in a wide set of fields, including physics, biology and business-oriented processes (such as financial prediction or optimized system-configuration selection). For some application contexts, one relevant aspect relates to the timeliness according to which simulation results are provided to end-users or applications, such as when exploiting simulation as a tool supporting time-critical decision making. Hence, performance aspects while delivering simulation output is a core issue to cope with. In the next sections we overview the typical approach used to achieve high performance simulation in the context of discrete event models, namely Parallel Discrete Event Simulation (PDES), posing the attention to the PDES optimistic synchronization mechanism, which forms the base ground for the thesis. Then, we present an overview of the specific problems targeted by the thesis and of the achieved outcomes.

#### 1.1 Parallel Discrete Event Simulation

In the context of Discrete Event Simulation (DES), high performance has been targeted via the Parallel-DES (PDES) paradigm [Fujimoto(1990)], which allows exploiting the computing power offered by (high-end) parallel/distributed platforms in order to speedup model execution and to make (very) large and/or accurate models tractable. The basic idea underlying PDES is to partition the simulation model into several distinct simulation objects, which are the core of the simulation process from the model writer's point of view. In fact, each object represents a portion of the real world being simulated, the evolution of

which is described by object state transitions, driven by a set of logical/mathematical properties. In order to represent real-world interactions, simulation objects can communicate with each other, by exchanging pieces of information in the form of events. From a technical point of view, simulation objects are handled by Logical Processes (LP), which undertake the concurrent execution of simulation events. Traditionally, a PDES run entails a number of concurrent LPs, uniquely identified by a numerical code in the range [0, N-1], and the overall simulation model keeps track of the evolution of the simulated world by relying on a global simulation state, which is partitioned into various LPs' private and disjoint simulation states  $^1$ .

In PDES, simulation events are timestamped and their execution is impulsive, meaning that there is no notion of time evolution during an event processing. The current simulation time at each individual LP is known as Local Virtual Time (LVT), and can be expressed in any measure unit (i.e., one LVT unit can represent seconds, hours, or even years, depending on the actual simulation model). This notion of time is opposed to the Wall-Clock Time (WCT), which is the actual notion of time we are used to. Therefore, in one WCT unit, the LVT advancement can be of one or several units, depending on the actual complexity of the simulation model and on the efficiency of the simulation run.

During the execution of an event, other events can be generated, destined to any simulation object in the system, and are associated with a timestamp value which is greater than or equal to the one of the event currently being executed, i.e. during the execution of the event  $e_x$  associated with the timestamp  $t_x$ , a new event  $e_y$  associated with timestamp  $t_y$  can be generated and sent to another simulation object, ensuring that  $t_y \geq t_x$ . Therefore, event generation evolves according to a causality pattern where the present cannot affect the past.

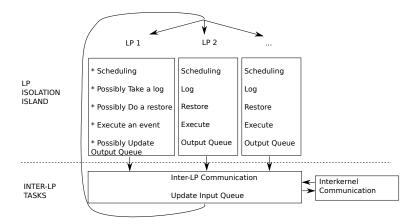

LPs are in charge of delivering simulation events to the hosted simulation objects, via the invocation of proper event handlers. Simulation-kernel instances take care of the dispatching event processing activities across the various LPs, and of managing inter-LP communication. In particular, they handle the LPs' event queues, by reflecting the updates associated with incoming messages, and determine the best LP to be dispatched in order to optimize specific execution metrics.

On the other hand, when running the LPs concurrently on multiple CPU-

<sup>&</sup>lt;sup>1</sup>Some approaches have studied variations where some portion of the state is shared across multiple LPs [Pellegrini et al.(2012)Pellegrini, Vitali, and Quaglia, Ghosh and Fujimoto(1991)]. However, the traditional case of disjointness of the LPs' states represents the most studied and exploited approach.

cores provided by the underlying parallel/distributed platform, synchronization mechanisms are required in order to ensure that the causality pattern is maintained not only for event generation but also for actual event processing at any LP. Although differentiated approaches to the definition of causally consistent execution have been devised in literature [Madhava Rao et al.(Dec)Madhava Rao, Thondugulam, Radhakrishnan, and Wilsey, Quaglia and Baldoni(1999), Fujimoto(1999), Cai et al.(2005)Cai, Turner, Lee, and Zhou], the most widely known and exploited causality criterion expresses that model execution is correct if each LP processes its input events in non-decreasing timestamp order.

To maintain causal consistency (namely local timestamp ordering at any individual LP) two main approaches have been proposed: conservative and optimistic. The conservative approach consists in avoiding at all the possibility of a causal violation, i.e., it can not happen that an event is executed out of order. To support this synchronization approach, block-until-safe policies are employed, which suspend event processing activities at an LP until it is determined that the execution of the next pending event is coherent with logical-time ordering. On the other hand, with the optimistic approach, event execution is never suspended at any LP, hence giving rise to speculative processing, under the optimistic assumption that causality is not violated. If any violation is detected, rollback recovery mechanisms are used to bring the involved LPs back to a correct state snapshot, starting from which execution of is resumed.

Literature results show that the optimistic approach is prone to higher parallelism exploitation, and to deliver performance which is less influenced by the message (event) delivery delay and by the lookahead within the simulation model <sup>2</sup>. These advantages are reflected also on the side of scalability, as demonstrated by the study in [Carothers and Perumalla(2010)], where very large platforms (entailing on the order of thousands of CPU-cores) are employed for a comparative analysis of conservative vs optimistic approaches. By this study, it clearly emerges that the conservative approach delivers better performance only for (very) high look-ahead values, which represent relatively uncommon cases. Further, such an advantage is reduced as the number of CPU-cores gets increased. Overall, better scalability of the optimistic approach in general contexts has been demonstrated.

<sup>&</sup>lt;sup>2</sup>The lookahead expresses the capability of a model to predict the non-occurrence of events within an given interval of simulated time, starting from the current time.

### 1.2 Optimistic Synchronization Overview

In this section we provide an overview of optimistic synchronization, such as the Time Warp protocol presented in [Jefferson(1985)]. The overview is tailored to the description of basic dynamics proper of the optimistic approach, and of some details that are more closely related to the specific topics of interest for this thesis. A deeper discussion on literature results coping with the topics addressed by the thesis is delayed to Chapter 2.

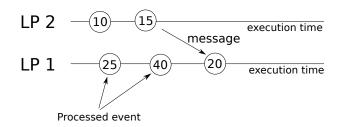

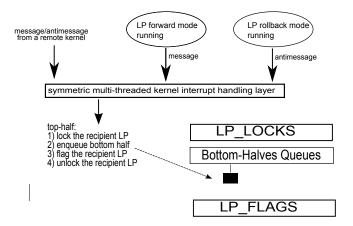

As hinted before, the optimistic approach aims at full exploitation of the parallelism offered by the underlying computing platform, which is achieved via the avoidance of block-until-safe policies for event execution, and on the adoption of speculative processing. With this approach, causality violations can occur upon the delivery of a so called straggler message to any LP involved in the run. A straggler message carries a scheduled event associated with a timestamp  $t_1$  which is lower than the timestamp  $t_2$  of some event that has already been processed by the recipient LP. In other words, the destination LP ran far ahead in simulation time with respect to some event that should have instead affected its evolution (an example of this situation is shown in Figure 1.1). In such a case, all the events that have already been processed by the recipient LP, having timestamp t included in the interval  $t_1 < t \le t_2$  are no longer causally consistent (with respect to the local timestamp ordering criterion).

Anytime a causality violation is detected, some rollback recovery mechanism needs to be actuated which involve, at the same time, two orthogonal issues:

- restoring the state of the rolling back LP to a past snapshot that is still consistent;

- undoing the effects of inconsistent local processing activities on other LPs.

The task in the last item is generally supported via the employment of so called anti-messages, which are used to annihilate events that have been scheduled by the rolling back LP as a result of causally inconsistent processing activities. An anti-message is therefore a negative copy of a previously sent message, and is used to signal the destination to discard the original message. Clearly, in case the event carried by the original message was already processed by the destination LP, we experience a spreading of the rollback occurrence along a chain of LPs (this phenomenon is also known as *cascading rollback*).

We note that messages (events) are inserted within the system by usually employing proper APIs offered by the underlying simulation environment as a support of typical PDES programming models. This implies that the

management of anti-messages upon the occurrence of rollback does not pose particular transparency problems with respect to the application-level code. In fact, the environment can log outgoing messages and generate the corresponding anti-messages if requested (e.g. by marking a "sign" bit within the messages' meta-data). As a consequence, research efforts in the management of anti-messages are primarily related to reducing the management overhead and the need for actually sending out the anti-messages associated with given messages, such as when employing "lazy cancellation" schemes [Gafni(1985)] <sup>3</sup>.

On the other hand, recoverability of the LPs' states poses problems on the side of both performance and application transparency. As for performance, we need to consider both CPU usage for supporting tasks enabling state recoverability and actual state recovery actions, as well as memory usage for keeping recoverability related data/meta-data. On this side, a wide literature exists that has proposed the employment of log/restore techniques (see, e.g., [Bellenot(1990), Preiss et al.(1994)Preiss, Loucks, and MacIntyre, Palaniswamy and Wilsey(1993)]), where snapshots of the state of the LPs are taken according to some (infrequent) policy in order to optimize the tradeoff between log costs and restore latency 4. Also, these techniques deal either with non-incremental or incremental logging, the latter approach (see, e.g., Rönngren et al. (1996) Rönngren, Liljenstam, Ayani, and Montagnat, Santoro and Quaglia(2005), West and Panesar(1996)]) being also oriented to reduce the usage of memory for log buffers. On the other hand, transparency issues deal with supporting log/restore tasks with no need for having log/restore modules to be implemented within the application-level code (hence masking the actual synchronization paradigm to the application programmer). This is a non-trivial aspect since it relates to the flexibility according to which the application programmer is allowed to organize the data structures representing the LP state image. As an example, the reliance on dynamic memory usage at the application level requires the optimistic simulation platform to entail complex memory management mechanisms [Toccaceli and Quaglia(2008)] in order to be able to make generic and scattered memory layouts to be recoverable

<sup>&</sup>lt;sup>3</sup>Lazy cancellation, as opposed to aggressive cancellation, tends to avoid sending out an anti-message as soon as an original message is detected to have been produced by out-of-order computation. This helps reducing the spreading of rollback in case the message would have been reproduced after resuming computation.

<sup>&</sup>lt;sup>4</sup>Taking a snapshot of the LP state less frequently increases the likelihood that the state to be restored is not logged, hence must be reconstructed by starting from a previous logged snapshot via fictitious re-processing of intermediate events. This re-processing phase is also known as *coasting forward*.

transparently and efficiently. On the other hand, this problem is exacerbated in case the target is incremental logging, since such a memory layout needs to be managed also on the side of identifying updates occurring within it, at a granularity level that allows providing advantages with respect to logging the whole state image. Recently, the memory demand problem associated with logging has been also tackled via so called reverse computing approaches [Carothers et al.(1999b)Carothers, Perumalla, and Fujimoto], where a state-restore operation is supported via application-level compensation logic that applies backward computation steps until the correct snapshot for resuming the LP is built. For this approach we still find issues in relation to how to generate the reverse code version transparently to the application programmer.

Still in relation to memory usage and recovery, optimistic synchronization is intrinsically linked to the notion of Global Virtual Time (GVT). It represents the commit horizon of the optimistic simulation run, namely the simulation time barrier currently separating the set of committed events from the ones which can still be subject to a rollback. This barrier corresponds to the minimum timestamp of not-vet-processed or in-transit messages/anti-messages, hence it is typically computed via global reduction protocols, which can be optimized for specific platform organizations (e.g., shared-memory systems vs clusters [Bauer et al.(2005)Bauer, Yaun, Carothers, Yuksel, and Kalyanaraman, Fujimoto and Hybinette(1997), Riley et al.(2000)Riley, Fujimoto, and Ammar]). Once the new GVT is available, all the memory buffers keeping the events that have been committed and the state logs related to the committed portion of the simulation can be released <sup>5</sup>. The procedure of recovering memory buffers is usually termed fossil collection. We note that the GVT protocol cannot be executed with unbounded frequency since it imposes overhead. This leads to further exacerbating the memory demand problem in optimistic simulation platforms, since they are requested to allocate and (temporarily keep) memory for information related to both speculative outcomes (e.g. speculatively scheduled events) and already committed actions (i.e. already committed events). Particularly, this may impose large memory usage especially for LPs' event and message queues, given that on the side of state recoverability infrequent logging and/or incremental schemes and/or reverse computing already tend to reduce such memory demand.

An additional central point in optimistic simulation platforms relates to the CPU-scheduling approach used to determine which LP, among the ones

<sup>&</sup>lt;sup>5</sup>For infrequent logging schemes, the only exception is related to the need for keeping data/meta-data for at least one logged state image with time t less than GVT, and the events with time in between t and the GVT value, in order to be able to recover the LP state image to any point in time arbitrarily close, or coinciding with, the GVT value.

hosted by a given simulation-kernel instance, must take control for actual event processing activities. Although several proposals have been made [Som and Sargent(1998), Quaglia and Cortellessa(2002), Rönngren and Ayani(1994a), Palaniswamy and Wilsey(1994)], the common choice is represented by the Lowest-Timestamp-First (LTF) algorithm [Lin and Lazowska (1991)]. It selects the LP whose next pending event has the minimum timestamp, compared to next pending events of other LPs hosted by the same kernel. Coupled with the traditional single-threaded approach for the implementation of the simulation kernel, LTF has the advantage of avoiding the generation of causality violations across the LPs hosted by the same kernel instance. This is because these LPs are dispatched in a way similar to what would happen on top of a sequential simulation engine, which imposes a timestamp-ordered sequence of CPU-schedule operations for all the events (across all the LPs). Hence, rollbacks can be generated only in relation to events scheduled between LPs hosted by different kernels, which contributes to reduce the amount of rollbacks, and to make the optimistic paradigm effective.

On the other hand, another aspect that can potentially hamper performance, due to excessive generation of rollbacks (possibly giving rise to thrashing phenomena), is the unbalanced advancement in simulation time of LPs hosted by different kernel instances. In other words, the optimistic paradigm needs to be complemented by proper mechanisms aimed at making computing resources exploited for fruitful simulation work (not for work that is eventually rolled back, thus only causing waste of resource usage). Waste of computing resources can also be observed on long-distance basis, namely when the final portion of the computation has no inter-kernel messages exchanges. In such a scenario, the less-loaded kernels would terminate sooner with respect to others, and the associated computing resources may remain unused until the termination of the slower kernel. Similar under-utilization scenarios may occur in case some kernel instance hosts LPs that have no event to process for a specific simulation time interval. In such a case, the computing power assigned to that kernel instance remains unused for a while (namely for the wall-clock-time period required for repopulating the event queues of those LPs, depending on proper dynamics of the simulation model). Beyond traditional load-balancing solutions [Glazer and Tropper(1993), Carothers and Fujimoto(2000), Jiang et al.(1994) Jiang, Shieh, and Liu, Peluso et al.(2011) Peluso, Didona, and Quaglia, the issue of balanced advancement in simulation time across different kernel instances has also been tackled via variants of the optimistic approach based on reduction of the level of optimism (hence reduction of the possibility for some LPs to run excessively ahead of others) [Srinivasan and Reynolds (1998), Ferscha (1995). The tradeoff provided by these approaches usually leads to reducing the likelihood of causality violation via reduction of the exploitation of the available computing power (the typical case is when

Figure 1.1: Straggler Message

execution of some LPs is explicitly throttled).

#### 1.3 Thesis Contributions

Along the line of the provided overview on optimistic synchronization, we can identify the contributions by this thesis as related to three core topics:

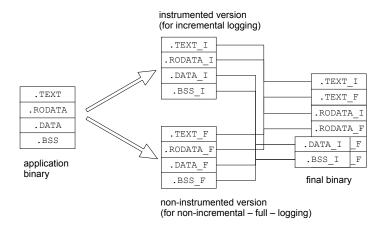

State log/restore: as for this topic (see Chapter 4), we present a fully innovative state log/restore architecture, which allows time interleaved co-existence of incremental and non-incremental log/restore operating modes on a per LP basis. The architecture is based on a dual-coding scheme, which is fully transparent to the application-level programmer, and enables the application code to rely on most of the ANSI-C standard. Dual coding is achieved via instrumentation of the ELF associated with the application, hence it is tailored for UNIX based systems. Further, the architecture performs the dynamic selection of the best-suited log mode (and of its optimal parameterization, e.g., in terms of frequency of the log operation) on the basis of an innovative analytical approach, which complements existing literature results.

Buffer delivery: as for this topic (see Chapter 5), we provide an innovative buffer-delivery architecture which is explicitly oriented to reduce the impact of virtual memory usage by the simulation platform on the effectiveness of the caching hierarchy. The architecture is based on a characterization of buffer access patterns proper of the optimistic paradigm, which we also propose within the thesis. Essentially, the architecture reserves a cache partition to hot data, favoring the residence in cache of part of the working set. Although this solution is generally applicable in different architectural contexts, it gives rise to a reduction of the bus contention, which is especially relevant in multi-core and multi-processors architectures.

13

Balanced resource usage: as for this topic (see Chapter 6), we present a reshuffle of the design approach of optimistic simulation platforms in order to generate a final architecture oriented to maximizing the exploitation of the computing power offered by multi-core machines in order to perform fruitful work. The reshuffle is based on a symmetric multi-threading paradigm, which allows supporting load-sharing policies (as opposed to traditional load-balancing) suited for enabling balanced advancement of the LPs along the simulation time axis with no need for migrating them. Specifically, the approach that has been taken is based on dynamic reassignment of the computing power to the active kernel instances. A specific load sharing policy, based on an analytical model of the expected computing power requested to sustain the workload by the different kernel instances, is also provided.

## Chapter 2

# Literature Survey

In order to frame the contributions by this thesis within literature results, a sight on what is the state of the art in relation to the addressed topics is provided. Particularly, we start with an overview of results dealing with state recoverability. Then we discuss approaches explicitly oriented to cope with memory demand in optimistic simulation platforms. Finally we discuss literature solutions aimed at balanced and fruitful usage of the computing resources in optimistic synchronization, including more recent approaches based on the concept of multi-threading.

### 2.1 State Recoverability

As hinted, one main means to support recoverability of the LP state in optimistic simulation systems is represented by logging approaches, where the state image is (infrequently) logged in order to generate restoration points along the simulation time axis. Several studies in this direction have been aimed at providing analytical models describing the expected log/restore overhead when experiencing a given rollback pattern (e.g. in terms of frequency of rollback occurrence at the LP) and when taking state logs, namely checkpoints, at specific points of the execution (for instance each  $\chi$  event executions, according to a periodic scheme) [Rönngren and Ayani(1994b), Lin et al.(1993)Lin, Preiss, Loucks, and Lazowska, Quaglia(2001)]. By monitoring the independent parameters appearing within the analytical expressions, the models can be used to (dynamically) determine the position of checkpoints in order to keep the whole log/resore overhead at minimum values. We recall that a lower number of checkpoints taken along a given execution path reduces the log cost, but is

expected to give rise to an increase in the restore cost. Particularly, the state to be recovered might not be immediately available within the log, and would need to be reconstructed by restoring an older snapshot and by reprocessing the intermediate events up to the target restoration point. Hence, the aforementioned approaches provide models for determining the well-suited balance among these two opposite overhead tendencies.

The provided models deal either with the case of non-incremental logging or with incremental logging, and some of them even cope with the case where the two approaches are used in combination (e.g. by taking incremental logs between subsequent non-incremental logs) [Soliman and Elmaghraby(1998)] or are considered comparatively [Palaniswamy and Wilsey(1993)]. However, these proposals have been mainly tailored to the evaluation of log/restore policies (once known the costs for basic operations, such as the copy of the whole or part of the LP state image into the log buffer), not to provide log/restore architectures explicitly tackling transparency of log/restore tasks to the application level code.

The issue of transparency has been dealt with by other studies. For incremental log/restore schemes this has been done by either instrumenting application level code (in order to transparently insert code portions aimed at identifying the write operations occurring onto the state image, thus allowing identification of the dirty portions of the state) [West and Panesar(1996)] or by employing operator overloading schemes, as for the case of the proposal in [Rönngren et al. (1996) Rönngren, Liljenstam, Ayani, and Montagnat] which has been tailored to object oriented technologies. For both the provided approaches there is anyhow the need for compile time identification of the memory portions forming the actual state image of the LP. Hence the approaches are not fully suited for supporting a general programming model where the memory layout of the LP state can rely on, e.g., dynamic memory allocation and/or can be updated via third party libraries. On the other hand, the solution in [Toccaceli and Quaglia(2008)] provides supports for transparency in the context of dynamic memory based state layouts, but limitedly to the case of non-incremental logging.

Other proposals have provided log architectures based on specialized hardware [Quaglia and Santoro(2003), Fujimoto et al.(1992)Fujimoto, Tsai, and Gopalakrishnan], which have been designed in order to achieve some level of transparency, while also offloading the CPU, at the price of limiting the programming model, e.g., by imposing contiguousness or static determination of the memory area maintaining the state image of the LP.

The case of dynamic memory usage at the application level has been addressed by the proposals in [speedes(), Das et al.(1994)Das, Fujimoto, Panesar, Allison, and Hybinette], which provide recoverability for memory scattered LP state images. However, the level of transparency is not maximized since

ad-hoc dynamic memory allocation/deallocation APIs are used to notify the underlying simulation platform that the corresponding operation needs to be rollbackable.

Full transparency, in combination with incremental logging, has been provided by the proposal in [Santoro and Quaglia(2005)], which has been tailored to parallel/distributed simulation platforms adhering to the High-Level-Architecture (HLA) specification [IEEE Std 1516-2000 (2000)(2000)]. This approach exploits a page-based memory update tracking mechanism relying on facilities (e.g. SEGFAULT tracking) offered by the underlying operating system. Hence the granularity according to which incremental logs are taken cannot be set arbitrarily, and cannot be optimized depending on the actual needs. Overall, these proposal are mostly suited for federations of simulation components where a middleware layer (namely the HLA Run-Time-Infrastructure) is used to operate distributed coordination and data exchange, whose overhead tends to mask the one imposed by the page-based logging approach. They result less suited for traditional PDES platforms, relying on highly optimized low-overhead engine level coordination and data exchange facilities.

An approach to state recoverability which is orthogonal to the aforementioned solutions has been provided in [Carothers et al. (1999b) Carothers, Perumalla, and Fujimoto. Instead of relying on state logs, this proposal is based on reverse computing schemes where the forward execution code (namely the native implementation of the application level simulation code) is coupled with a reverse code version which is in charge of backward compensating (hence undoing) the updates occurred onto the LP state in case a rollback occurs. The issue of automation of the generation of the reverse code, which targets transparency to the application programmer, is also faced. The reverse computing approach has been recently exploited, and has been demonstrated to be effective, for several applications [Bauer and Page(2007), Seal and Perumalla(2011). Particularly, one main advantage by this approach is the reduction of memory demand for state-log buffers, while also nullifying the log overhead (since logs are not taken at all). On the other hand, the tradeoff is towards a potential increase of the restore latency in case very long rollbacks occur, which would require log reverse computing paths to achieve the restoration point. On the other hand, this approach can be complemented with periodic state logging in order to both (a) avoid excessively log backward computation phases, and (b) to deal with non-reversible operations (such as flat assignments within the state image).

Advancement by the thesis. As for state recoverability, the thesis advances the state of the art by providing a log/restore solution, inspired to the

autonomic computing paradigm, which does not rely on any specialized hardware, and jointly addressed transparency and performance issues by exhibiting all together the following features:

- It allows the application level programmer to use standard constructs for dynamic memory allocation/deallocation operations, hence allowing the LP state to be scattered across non-contiguous memory chunks.

- It transparently enables phase-interleaved adoption of incremental and non-incremental log/restore modes.

- It runs each log/restore mode in a highly optimized fashion, via the adoption dual-coding approaches and of classical schemes for the optimization of typical parameters determining the actual overhead for each mode.

- It dynamically (and transparently) switches to the best suited operating mode (incremental vs non-incremental) depending on proper execution dynamics of the optimistic simulation run.

While individual, or subsets, of the above points are dealt with by literature results, none of these proposals fully covers the whole set of listed issues.

### 2.2 Memory Management

Although optimized approaches and/or architectures supporting state recoverability can also be considered as solutions aimed at reducing the memory demand by the optimistic simulation environment (this is especially true when considering reverse computing approaches), such a reduction can be considered as a reflection of the whole optimization process leading to well suited tradeoffs between log and restore overheads. On the other hand, the memory demand problem in optimistic simulation platforms, and its reflection on the effectiveness of the underlying caching hierarchy and virtual memory system, have also been addressed via sector specific approaches.

As hinted, the memory demand by optimistic platforms does not only involve log operations, but the need for temporary maintaining events that are not yet detected as already committed (since GVT is typically re-evaluated periodically), and the need for supporting speculative scheduling of future events. The latter aspect may entail high frequency for buffer allocation requests just due to the fact that purely optimistic approaches can allow the LPs to run far ahead of the currently committed horizon given the absence of blocking or throttling strategies.

As for memory requirements related to the already committed portion of the computation, some advanced fossil collection mechanisms have been proposed [Chetlur and Wilsey(2006)] that, by means of dissemination of information about causality relations among events, are aimed at the identification of the fossils (hence of memory to be recovered) in an complementary manner compared to the classical ones based on GVT computation.

The effects of the caching hierarchy and of the underlying virtual memory system on the performance of specific tasks (such as state saving) and/or of the overall simulation run has also been studied by several works [Carothers et al.(199a)Carothers, Perumalla, and Fujimoto, Akyildiz et al.(1993)Akyildiz, Chen, Das, Fujimoto, and Serfozo, Akyildiz et al.(1992)Akyildiz, Chen, Das, Fujimoto, and Serfozo, Das and Fujimoto(1997a)]. Outcomes by these studies show how both caching and virtual memory may have a relevant impact on performance, thus posing the need for optimizing platform level configuration and/or design in order to limit the performance degradation phenomenon.

Interesting proposals aimed at the integration of advanced memory management schemes specifically tailored to optimistic PDES platforms can be found in [Lin and Preiss(1991), Das and Fujimoto(1997b), Jefferson(1990), Preiss and Loucks(1995)]. Here the authors propose techniques, such as cancelback, pruneback or artificial rollback, which are aimed at achieving efficient executions of the optimistic paradigm when considering limited available memory. This is achieved by, e.g., artificially squashing portions of speculated computation in order to avoid maintaining the related information (such as the record for speculatively scheduled events) when memory demand becomes critical (such as when swapping phenomena within the virtual memory system would tent to appear). With this type of integrations, the optimistic approach has been shown to be able to complete the run at reasonable performance by using an amount of memory similar (or slightly larger than) the one requested by a sequential, non-speculative run of the same simulation application. Further, the performance tradeoffs associated with these schemes have been thoroughly investigated both analytically and empirically (see, e.g., [Das and Fujimoto(1993)]).

Different approaches, still tailored to the tradeoff between memory management and performance, relate to the reduction of the number of memory copies for supporting event exchanges within the optimistic platform. Particularly, the proposal in [Swenson and Riley(2012)] provides a so called zero-copy message passing approach, suited for both conservative and optimistic simulation, which allows reducing the whole memory demand due to message buffering on shared memory architectures, thanks to the reduction of the amount of virtual memory buffers used for keeping the messages.

The only work in literature that directly faces the cache hierarchy misuse in optimistic simulators is [Fuj95], whose main target is to point out the rele-

vance of buffer delivery mechanisms that are cache-friendly in shared memory contexts. The work exclusively accounts for buffers reserved for exchanged messages. It presents a new approach that partitions the memory destined to messages in a way that the pages are accessed only by the two processes that participate in the communication, providing a reduction of the cache-coherence overhead and the cache invalidation. Our proposal is orthogonal since it does not account for message-related buffers only, and can be deployed on both shared and non-shared memory platforms.

Advancement by the thesis. In this thesis we address the effects on performance due to the memory system in an orthogonal manner with respect to all the aforementioned solutions. Particularly, we concentrate on caching phenomena and propose an innovative architecture which supports a cacheaware memory delivery mechanism specifically tailored to optimistic simulation platforms. Hence our approach could be used in combination with other approaches which have been targeted to the reduction of virtual memory usage by the platform.

We must say that cache-aware memory allocation is not a new topic in general (namely, outside the PDES area). However, our approach differs from existing solutions. As an example, when considering cache-aware buffer delivery within operating system kernels (such as the LINUX Slab-allocator [Bonwick(1994)]), the main objective is the minimization of the RAM/cache data movement (e.g. via the minimization of false cache sharing on multi-core machines). Compared to these approaches, we further target the concept of hot vs cold data in the context of optimistic simulation runs, and tailor cache usage in order to optimize the management of hot data (namely buffers associated with information that requires more frequent access).

As for the maximization of cache hits, some buffer allocation policies have been proposed in [Chilimbi et al.(2000)Chilimbi, Hill, and Larus]. These are based either on proper APIs to notify the memory management system that different memory areas are correlated in terms of expected future accesses (hence they should be located such in a way to be loaded into, e.g., the same cache line) or on run-time profiling mechanisms aimed at clustering memory accesses and reorganizing the layout to maximize cache efficiency. Compared to these approaches we do not require the usage of proper APIs (hence the simulation platform can rely on traditional memory allocation services) and do not require run-time profiling (hence we avoid the associated costs) since buffer relevance in terms of cache hits/misses are predefined via a general scheme tailored to optimistic PDES systems.

In terms of employed cache management methods, the work more close to our approach is the one in [Mueller(1995)] which presents a softwarepartitioned cache system to allow predictable task execution for real-time environments. However, the final target of this work is completely orthogonal to our one since it is focuses on memory latency predictability, achieved at the cost of performance drops caused by the non-minimal number of cache partitions that are typically required to support the different real-time tasks. Conversely our goal is to increase exploitation of the cache system, which is achieved by partitioning the cache to host buffers accessed in different execution patterns in two different cache partitions. The two-partition division reduces cache pollution due to infrequently accessed buffers, favoring the permanence of (part of) the working set in one of the two partitions.

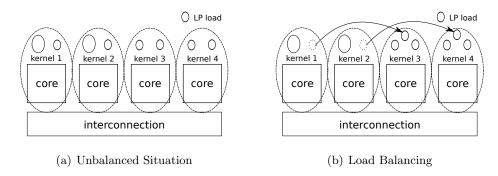

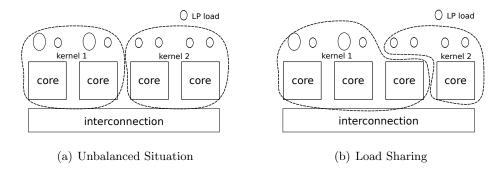

### 2.3 Balanced and Fruitful Usage of Resources

Balancing the usage of resources and its reflection on balanced and performanceeffective advancement in simulation time by different LPs is a fundamental issue to be addressed for both conservative and optimistic simulation systems. While in conservative simulation a non-balanced scenario could lead to underutilization of the resources, in optimistic simulation platforms we may also experience thrashing phenomena due to excessive rollback generation. This issue has been traditionally tackled via load-balancing schemes where the LPs are dynamically migrated from one simulation kernel instance to another depending on the actual load they impose in a specific phase of the simulation run. Along this direction we can find several solutions, such as [Glazer and Tropper (1993), Carothers and Fujimoto (2000), Choe and Tropper (1999), Meraji et al. (2010) Meraji, Zhang, and Tropper, which share the common feature of being targeted to provide metrics for detecting imbalance scenarios and policies to re-balance the load, but that are not targeted to provide architectural solutions for full transparency of the LP migration task to the application programmer. Other studies have addressed the issue of load re-balance in optimistic simulation systems for specific application fields, such as logic circuit simulation [Meraji and Tropper(June)], hence providing sector specific policies.

As for transparency, a recent work in [Peluso et al.(2011)Peluso, Didona, and Quaglia] provides a global memory management architecture that allows reinstalling the LP state image (even in case it is formed by memory scattered dynamically allocated chunks) across different kernel instances with no intervention by the application level code. The architecture has been then combined with already existing balancing policies (particularly the one in [Carothers and Fujimoto(2000)]) in order to provide fully fledged supports for the re-balance problem in general application contexts.

All the above approaches have been targeted to scenarios where the dif-

ferent kernel instances can be run on either shared memory or distributed memory systems. Hence they do not explicitly consider the possibility of exploiting the actual sharing of memory across different processes/threads within the simulation platforms. Given the relevance of the multi-core architectural organization, which natively offers sharing facilities, more recent approaches have been tailored to balanced and fruitful resource usage in the context of shared-memory platforms.

Along this path, the work in [Chen et al.(2011)Chen, Lu, Yao, Peng, and Wu] presents a global schedule mechanism relying on a distributed event queue that can be accessed by different threads, which is used to fairly distribute the actual simulation load across the whole set of CPU-cores within the underlying platform. However, the global event queue represents a synchronization point which tends to hamper scalability of the proposed solution. In fact, the effectiveness of the approach has been tested limitedly to the case of a maximum of 8 CPU-cores. Similar considerations can be made for the case of the ThreadedWarped architecture in [Miller(2010)], which uses a global priority queue across subsets of the threads within the platform. While this approach reduces contention (given that a queue is shared by a subset of threads, rather than all the active ones), it does not allow to redistributed the load (i.e. the LPs) across different subsets of threads. Hence, execution of a specific LP remains confined onto a given subset of the CPU-cores within the platform.

Finally, one recent work specifically oriented to improve the performance of simulation platforms on multi-core machines can be found in [Liu and Wainer(2012)]. This work is targeted at the IBM Cell processor [Kahle(2005)], thus not being immediately suited for differentiated multi-core platforms.

Advancement by the thesis. As for balanced and fruitful usage of resources, the thesis provides an innovative approach explicitly targeted to multicore machines, which is based on a paradigm shift from load-balancing to load-sharing. Particularly, in our proposal, a simulation kernel instance is a dynamic entity structured according to a symmetric multi-threaded paradigm, which has the ability to acquire or release computing power depending on the actual workload to be sustained. As a result, the hosted LPs can potentially run on any CPU-core (given that any core can be incorporated for usage by the kernel instance hosting the LP). Hence higher flexibility is provided in terms of mapping of LPs to CPU-cores, and hence in terms of determining a well suited balance of the whole workload over the underlying platform.

We note that this approach is fully orthogonal to load-balancing, hence they could be used in combination, for example for optimizing resource usage in clusters of multi-core machines (where load-sharing can optimize intramachine dynamics, while load-balancing and the associated LP migration schemes can optimize inter-machine dynamics).

Finally, we note that the architectural proposal for the reshuffle to loadsharing has been also complemented with an innovative analytical model for the determination of how to reassign the computing power to the different kernel instances, which constitutes an additional contribution by the thesis.

# Chapter 3

# Reference Environment

In this chapter we illustrate the hardware and software environment that has been exploited for integrating and experimentally evaluating the proposals by this thesis. We will start by over-viewing the hardware platform and the lower-level software facilities (such as the operating system and the used compiling tools). Then we present the target open source optimistic simulation platform where the solutions provided by the thesis have been integrated, namely ROOT-Sim. Finally, we describe the applications that have been used as benchmarks in the experimental studies.

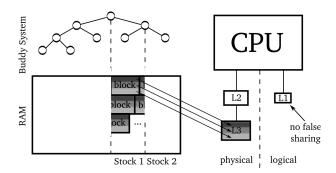

#### 3.1 Hardware and Base Software

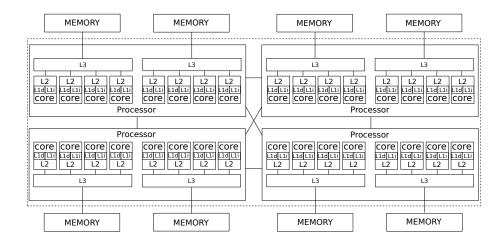

Our reference computing platform is an HP ProLiant server equipped with four 2GHz AMD Opteron 6128 processors working at 64-bits. Each processor is composed by 8 cores, for a total amount of 32 cores. Each core has a private 128 KB L1 cache (64 KB data-cache and 64 KB instruction-cache) and a private 512KB L2 cache. The last level of cache (LLC), having 5118 KB capability, is shared among four cores within a single processor, for a total of 10236 KB within the same processor. The machine is equipped with 64 GB of RAM based on a NUMA (Non-Uniform Memory Access) architecture, where each group of cores that share the LLC sees 8 GB as *close memory* and the remaining 56 GB as *far memory* <sup>1</sup>. The schematized machine-architecture is

<sup>&</sup>lt;sup>1</sup>In NUMA architectures several CPU-cores share memory resources, and the memory is split in a way that each bank is "close to" a subset of the CPU-cores, commonly called node. Each node accesses its close memory banks in fast way, while slower access is experienced for

Figure 3.1: Schematized machine architecture

|                         | L1 Data | L1 Inst     | L2      | L3               |

|-------------------------|---------|-------------|---------|------------------|

| Ways of associativity   | 2       | 2           | 16      | 48               |

| Type                    | Data    | Instruction | Unified | Unified          |

| Size (KB)               | 64      | 64          | 512     | 5118             |

| Coherence line size (B) | 64      | 64          | 64      | 64               |

| Shared vs Private       | Private | Private     | Private | Shared (4 cores) |

Table 3.1: Opteron cache details

shown in Figure 3.1, while details related to the caching system are provided in Table 3.1.

The operating system installed on the machine is 64-bit Debian 6, with Linux Kernel version 2.6.32.5. The compiling and linking tools that have been exploited are gcc 4.3.4 and binutils (as and ld) 2.20.0.

memory banks that are close to others node. The access type is called non-uniform because all the nodes see the whole memory, but each node accesses different memory portions with different latencies.

#### 3.2 The ROOT-Sim Platform

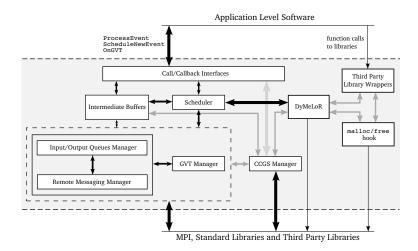

The simulation platform that has been taken as the reference for integrating all the proposals by this thesis is the ROme OpTimistic Simulator (ROOT-Sim) [Pellegrini et al.(2011)Pellegrini, Vitali, and Quaglia, HPDCS Research Group(2012)]. This is a C/MPI-based open source optimistic simulation platform based on the Time Warp protocol [Jefferson(1985)] and tailored for UNIX-like systems. This platform has been designed as a general purpose solution, hence being suited for supporting differentiated simulation models adhering to a very simple programming model (as we shall also discuss in Section 3.2.1). The platform transparently handles all the mechanisms associated with parallelization, (e.g., mapping of LPs on different kernel instances) and optimistic synchronization (e.g., state recoverability). A schematization of the internal architecture of ROOT-Sim, as it was standing before integrating the proposals by this thesis, is shown in Figure 3.2.

At the core of the architecture, there is an event-queue manager that maintains multiple input/output queues storing incoming (or already processed) and outgoing simulation events. Each pair of input/output queues is logically associated with a same locally-hosted LP. The interaction between the event-queue manager and the MPI layer, in order to support event notification across different instances of the ROOT-Sim kernel, is mediated by a messaging manager which multiplexes ROOT-Sim defined message tags (e.g., EVENT or ANTI\_EVENT) travelling across different ROOT-Sim instances over the same MPI channel. The scheduling sub-system gives control to the application layer along the same thread running the scheduler. Hence, simulation events (and the associated LPs) are dispatched for execution according to a classical timeinterleaved mode, where the scheduling priority for the next-to-be-executed event across all the hosted LPs is based on the Lowest-Timestamp-First (LTF) algorithm. The scheduler can run in two differentiated modes. The first one is a stateless O(n) mode, resembling the linux-2.4 scheduler, which queries the event-queue manager at each dispatch operation for getting information about the next-event timestamp (and hence the scheduling goodness) of all the LPs. The second mode [Santoro and Quaglia(2010)] operates in constant time (at least statistically), and is based on pre-populated meta-data that are constantly kept updated by reflecting the updates of the input queues of the locally hosted LPs. It results well suited for (very) large models, for which the advantages in terms of reduced scheduling latency overstep any overhead for scheduler-state maintenance.

As for state recoverability (and hence of data structures maintained at the application level), which is a crucial aspect for the design of effective optimistically synchronized environments, two main architectural approaches have been adopted. First, dynamic memory allocation and release via the standard

Figure 3.2: ROOT-Sim architecture

malloc library are hooked by the kernel and redirected to a wrapper. Second, the simulation platform is "context-aware", i.e., it has an internal state which distinguishes whether the current execution flow belongs to the application-level code or the platform's internals. In the former case, the hooked calls are redirected via the wrapper to an internal Memory Map Manager (called DyMeLoR), which handles allocation/deallocation operations by maximizing memory locality for the state layout of each single LP, and by maintaining meta-data allowing the memory map to be recoverable to past values [Toccaceli and Quaglia(2008)]. This aspect will be further discussed in Chapter 4 since the internal architecture of DyMeLor has been exploited as a starting point for our autonomic log/restore proposal. Overall, thanks to DyMeLoR, ROOT-Sim complies to a model where an LP is a (dynamically allocated) set of data structures updated by subsequent calls to an event handler. This semantic will be maintained via the autonomic management.

Concerning GVT calculation, ROOT-Sim relies on an optimized asynchronous approach based on a message acknowledgment scheme to solve the well-known transient message problem. Within this scheme, each kernel instance keeps track of all the messages sent to the other instances in an aggregate manner (i.e., via counters). Also, to reduce the communication overhead, each instance sends cumulative acknowledgment messages according to a window-based approach. Finally, to overcome the simultaneous reporting problem, each kernel instance temporarily stops sending acknowledgment messages during the execution of the GVT protocol.

ROOT-Sim also supports a very peculiar service that, once a new GVT

value is available, transparently rebuilds a Committed and Consistent Global Snapshot (CCGS), formed by a collection of individual LPs' states (see [Cucuzzo et al.(2007)Cucuzzo, D'Alessio, Quaglia, and Romano]). This occurs via update operations applied to local committed checkpoints of individual LPs so to eliminate mutual dependencies among the final-achieved state values. The checkpoint update operation is completely transparent since ROOT-Sim realigns the logged state images by triggering the execution of event handlers natively present within the application code, by passing as input already committed events not yet discarded by memory recovery procedures. Once the CCGS is built, each LP gains control via an ad-hoc callback within the API, by also having access to the copy of its state image belonging to the CCGS. Such a service can support, e.g., termination detection schemes based on global predicates evaluated on a committed and consistent global snapshot.

#### 3.2.1 Exposed API

Beyond auxiliary functions, e.g., for accessing recoverable random number generators, ROOT-Sim supports the following API:

- (A) int ProcessEvent(int me, time\_type now, int event\_type, void \*content, int size, void \*state) a callback to be implemented within the application layer, which provides control to the application for the actual processing of simulation events. me is the identifier of the LP being dispatched, now is the current value for the local clock, event\_type is the numerical code for the event to be processed, content is the buffer maintaining the event payload (made of size bytes), and state is the pointer to the top data structure forming the LP state layout.

- (B) int ScheduleNewEvent(int where, time\_type timestamp, int event\_type, void \*content, int size) this function allows injecting a new simulation event within the system, to be destined to whichever simulation object identified via where (the other parameters have the above described meaning).

- (C) int onGVT(int me, void \*snapshot) this callback passes control to the application by providing the LP snapshot belonging to the CCGS.

By the above description, it is clear that the application programmer is requested to reason on no aspect in relation to parallelism of the model execution. The programmer is only requested to understand that what is coded within the ProcessEvent callback will be executed speculatively. Hence, any audit on the simulation model state-trajectory (when considering committed state updates) will need to be carried out via inspection on the LPs' states

through the onGVT callback. No other aspect in relation to the actual execution mode and synchronization dynamics is seen by the programmer.

#### 3.2.2 Code Examples

In this section we present some code snippets to implement a working ROOT-Sim application which models a set of N nodes connected as a mesh, sending packets randomly to each other. The simulation model implementation is straitforward thanks to the fact that all the tasks related to parallelization or other housekeeping operations are completely hidden. The first important thing is to define the possible events handled by the model, the content of an event message, and the structure of the state:

Notice that in this application we allow just two events: INIT, sent by the simulation kernel to startup the simulation, and PACKET, which identifies the transit of a packet in the mesh. PACKETS is a macro that will be used in the termination check, while master\_seed is an initial seed for random functions exposed by the platform.

Then, we must specify the actual logic for the ProcessEvent() callback. This is the only entry point at application level for processing events, so we must rely on a switch construct to demultiplex them:

```

void ProcessEvent(int me, time_type now, int event_type,

event_content_type *event_content, void *ptr) {

event_content_type new_event_content;

lp_state_type *pointer = (lp_state_type*)ptr;

time_type timestamp;

switch(event_type) {

case INIT:

pointer = (lp_state_type *) malloc(sizeof(lp_state_type));

pointer->pckt_count = 0;

pointer->seed_state = master_seed;

timestamp = (time_type)(20*Random((unsigned long *) \

&pointer->seed_state));

ScheduleNewEvent (me, me, timestamp, PACKET, NULL, 0);

break;

case PACKET: {

pointer->pckt_count++;

new_event_content.sent_at = now;

int rcv = (N_PRC_TOT * Random((unsigned long *) \

&pointer->seed_state ) );

timestamp = now + (Expent(((unsigned long *) \

&pointer->seed_state), DELAY));

ScheduleNewEvent(rcv,me,timestamp,PACKET,\ \setminus

&new_event_content, size of (new_event_content));

}

}

}

```

The logic in the code is fairly simple: upon INIT event, the LP's state is malloc'd and initialized, and an initial packet is sent to the LP itself. Whenever a PACKET event is received, a local counter is increased, and a packet is sent back to a random LP in the simulation environment. Timestamps associated to these events are computed according to an exponential distribution, exploiting the internal Expent() function.

CheckTermination() is the second callback to be implemented in the application-level code, and it performs a local check on the LP's state. In particular, if the number of packets passed in the LP is smaller than PACKETS, it tells the simulation platform that the simulation cannot be halted yet:

```

int CheckTermination(lp_state_type *snapshot, int gid) {

if (snapshot->pckt_count < PACKETS)

return 0;

return 1;

}</pre>

```

## 3.2.3 ROOT-Sim audience

ROOT-Sim is a general purpose simulation platform, it implies that the possible audience is represented by eachone needs to perform a simulation. Its intrinsic parallelism make it suited in particular to be adopted when the model to simulate is complex, both from a computational point of view or from resource requirements one, or when there are some real-time constraints to be matched. The reduced API and the trasparency of all the housekeeping operations make it suited also by all that scientists who do not have good programming skills.

# 3.3 Benchmark Applications

We exploited two different benchmark applications in this thesis, namely:

- PCS (Personal Communication System), and

- Traffic

Both the applications are described in details in what follows.

#### 3.3.1 Personal Communication System

Personal Communication System (PCS) models a cellular (connected) network adhering to GSM technology, where each LP models the evolution of the state of an individual cell, and the whole set of cells provides wireless coverage on a square region of variable size (which depends on the total number of cells included in the model, each one assumed to cover an hexagonal region, as in typical modeling approaches [Boukerche et al.(1999)Boukerche, Das, Fabbri, and Yildz]). Each cell handles a parameterizable number N of wireless

channels, thus the whole model can be tailored for being representative of micro-cell vs macro-cell technology. Wireless channels are modeled in a high fidelity fashion via explicit simulation of power regulation/usage and interference/fading phenomena on the basis of the current state of the corresponding cell. The power regulation model has been implemented according to the results in [Kandukuri and Boyd(2002)].

The event types which can occur at any LP are:

- Start Call, which is intended to simulate a new call installation on a target cell;

- End Call which is intended to simulates a call termination;

- Handoff Leave which is intended to simulate the leave of an on-going call (i.e. of an active device) from the current residence cell;

- *Handoff Receive* which is intended to simulate the installation of a call handed-off from an adjacent cell;

- Recompute Fading, which is intended to simulate the effects of climatic variations onto the fading (and consequently interference) phenomena for ongoing calls.

Upon the start of a call destined to a mobile device currently hosted by a given wireless cell, a call-setup record is instantiated via dynamically-allocated data structures, which gets linked to a list of already active records within that same cell. Each record gets released when the corresponding call ends or is handed-off towards an adjacent cell. In the latter case, a similar call-setup procedure is executed at the destination cell. Upon call-setup, power regulation is performed, which involves scanning the aforementioned list of records for computing the minimum transmission power allowing the current call-setup to achieve the threshold-level SIR value. Data structures keeping track of fading coefficients are also updated while scanning the list, according to a meteorological model defining climatic conditions (and related variations). The climatic model accounts for variations of the climatic conditions (e.g. the current wind speed).

This application is highly parameterizable, so that several different configurations have been exploited in this thesis in order to better tailor the experiments to the specific objective. Beyond the already mentioned number N of wireless channels per cell, the set of configurable application parameters entails:

•  $\tau_A$ , which expresses the inter-arrival time of subsequent calls to any target cell;

- $\tau_{duration}$ , which expresses the expected call duration;

- $\tau_{change}$ , which expresses the residual residence time of a mobile device into the current cell, as evaluated since the time instant of installation of the call within the cell.

Different distributions can be used for determining samples of the above parameters, among which this thesis mostly rely on the exponential one.

A relevant dependent parameter within PCS models is the channel utilization factor, expressing the percentage of time during which the channel is busy. Particularly, the channel utilization factor depends on other parameters according to the following expression:

$$utilization factor = \frac{\tau_{duration}}{\tau_A * N}$$

The value of this parameter impacts the granularity of the events since the more the busy channels, the more power-management records are allocated and consequently scanned (or updated, as when fading gets recomputed on the basis of climatic variations) during the processing of different events. On the other hand, higher values of the channel utilization factor lead to higher memory requirements for the state image of individual LPs. Both the above dependencies (namely, CPU demand and memory) are anyhow bounded depending on the total number N of per-cell managed channels.

#### 3.3.2 Traffic

This application simulates a complex highway system (at a single car granularity), where the topology is a generic graph, where nodes represent cities or junctions and edges represent the actual highways. Every node is described in terms of car inter-arrival time and car leaving probability, while edges are described in terms of their length.

At startup phase, the simulation model is asked to distribute the highway's topology on a given number of LPs. Every LP therefore handles the simulation of a node or a portion of a segment, the length of which depends on the total highway's length and the number of available LPs.

Cars enter the system according to an Erlang probability distribution, with a mean interarrival time specified (for each node) in the topology configuration file. They can join the highway starting from cities/junctions only, and are later directed towards highway segments with a uniform probability. Whenever a car is received, it is enquequed in the LP's list of traversing cars, and its speed (for the particular LP it is entering in) is determined according to a Gaussian probability distribution, the mean and the variance of which are specified at startup time. Then, the model computes the time the car will

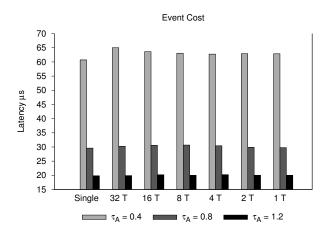

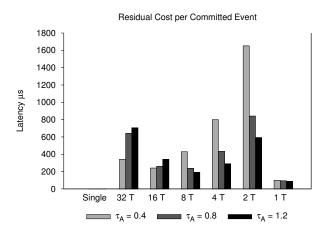

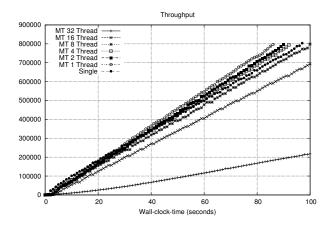

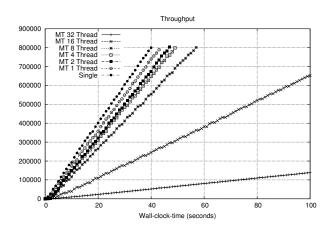

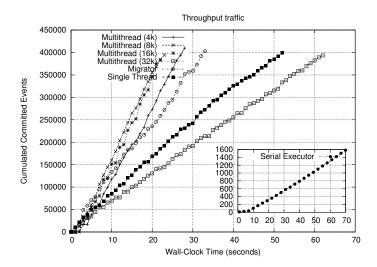

need to traverse the node, adding traffic slowdowns which are again computed according to a Gaussian distribution. In particular, the probability of finding a traffic jam is a function of the number of cars which are currently passing through the node.