### SAPIENZA UNIVERSITY OF ROME

Ph.D. program in Computer Engineering XXVI Cycle

## Autonomic Concurrency Regulation in Software Transactional Memories

Diego Rughetti

2014/3

### SAPIENZA UNIVERSITY OF ROME

Ph.D. program in Computer Engineering XXVI Cycle

### Diego Rughetti

## Autonomic Concurrency Regulation in Software Transactional Memories

#### Thesis Committee

#### Reviewers

Prof. Bruno Ciciani (Advisor) Prof. Giorgio Grisetti

Prof. Vincent Gramoli Prof. Jean-François Méhaut

2014/3

AUTHOR'S ADDRESS: Diego Rughetti Dipartimento di Ingegneria Informatica, Automatica e Gestionale Sapienza Università di Roma Via Ariosto 25, 00185 Roma, Italy e-mail: rughetti@dis.uniroma1.it

www: http://www.dis.uniroma1.it/~rughetti/

To my grandparents

## Contents

| 1        | Inti | coduction                                      | 7  |

|----------|------|------------------------------------------------|----|

| <b>2</b> | Sof  | tware Transactional Memories                   | 13 |

|          | 2.1  | Software Transactional Memories brief overview | 13 |

|          | 2.2  | The problem of concurrency in STM              | 15 |

| 3        | Per  | formance Optimization in STM, State of Art     | 27 |

|          | 3.1  | Approaches for performance optimization in STM | 31 |

| 4        | Ap   | plication Model and Workload Features          | 45 |

|          | 4.1  | Model of the STM application                   | 45 |

|          | 4.2  | STM application performance model              | 46 |

|          | 4.3  | Input parameters analysis                      | 47 |

|          | 4.4  | Input parameters - experimental data           | 50 |

| <b>5</b> | Ma   | chine Learning Based Approach                  | 55 |

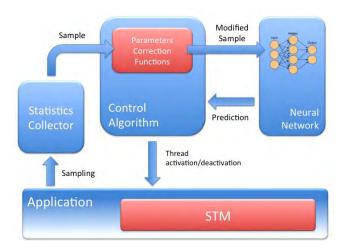

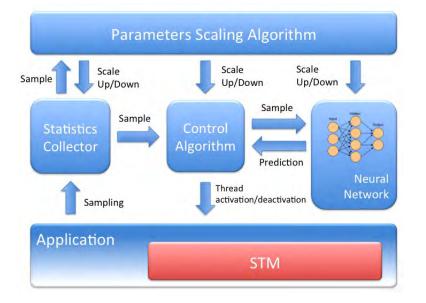

|          | 5.1  | System Architecture                            | 57 |

|          |      | 5.1.1 Controlling the Concurrency Level        | 59 |

|          | 5.2  | Implementation                                 | 63 |

|   | 5.3 | Exper  | imental Evaluation                                      | 65  |

|---|-----|--------|---------------------------------------------------------|-----|

|   |     | 5.3.1  | Evaluation Methodology                                  | 66  |

|   |     | 5.3.2  | Off-line Training                                       | 67  |

|   |     | 5.3.3  | Results                                                 | 70  |

|   | 5.4 | Sampl  | ing Overhead Optimization                               | 79  |

|   | 5.5 | Dynar  | nic feature selection                                   | 82  |

|   |     | 5.5.1  | Rationale                                               | 82  |

|   |     | 5.5.2  | Pragmatic Relevance: Run-time Sampling Costs $\ldots$ . | 85  |

|   |     | 5.5.3  | Shrinking vs Enlarging the Feature Set                  | 92  |

|   |     | 5.5.4  | The Actual Dynamic Feature Selection Architecture       | 95  |

|   | 5.6 | Exper  | imental Evaluation                                      | 98  |

| 6 | The | Analy  | ytical Model Based Approach                             | 107 |

|   | 6.1 | The P  | arametric Performance Model                             | 108 |

|   |     | 6.1.1  | Basic Assumptions                                       | 109 |

|   |     | 6.1.2  | Model Construction                                      | 109 |

|   |     | 6.1.3  | Instantiating $\rho$ , $\omega$ and $\phi$              | 111 |

|   |     | 6.1.4  | Model Validation with Respect to a Real System          | 122 |

|   | 6.2 | Concu  | rrency Self-Regulating STM                              | 127 |

|   |     | 6.2.1  | The Architecture                                        | 127 |

|   |     | 6.2.2  | Evaluation Study                                        | 130 |

| 7 | The | Hybr   | id Approach                                             | 135 |

|   | 7.1 | Perfor | mance Model Aim                                         | 137 |

|   | 7.2 | The A  | ctual AML Model                                         | 139 |

|   |     | 7.2.1  | Correcting Factors                                      | 145 |

|   | 7.3 | Exper  | imental Evaluation                                      | 147 |

|              |                | 7.3.1   | The AML Based Concurrency Regulation Architecture | 147 |

|--------------|----------------|---------|---------------------------------------------------|-----|

|              |                | 7.3.2   | Experimental Data                                 | 149 |

|              |                |         |                                                   |     |

| 8            | $\mathbf{STN}$ | As Per  | formance Comparison                               | 167 |

|              | 8.1            | Refere  | nce Architectures and Configurations              | 168 |

|              |                | 8.1.1   | SwissTM                                           | 168 |

|              |                | 8.1.2   | TinySTM                                           | 169 |

|              |                | 8.1.3   | TinySTM Adaptive Configurations                   | 170 |

|              | 8.2            | Experi  | imental Data                                      | 172 |

| 9            | Con            | clusio  | ns                                                | 185 |

| $\mathbf{A}$ | Net            | ıral Ne | etworks                                           | 191 |

| в            | The            | STAN    | AP Benchmark Suite                                | 195 |

# List of Figures

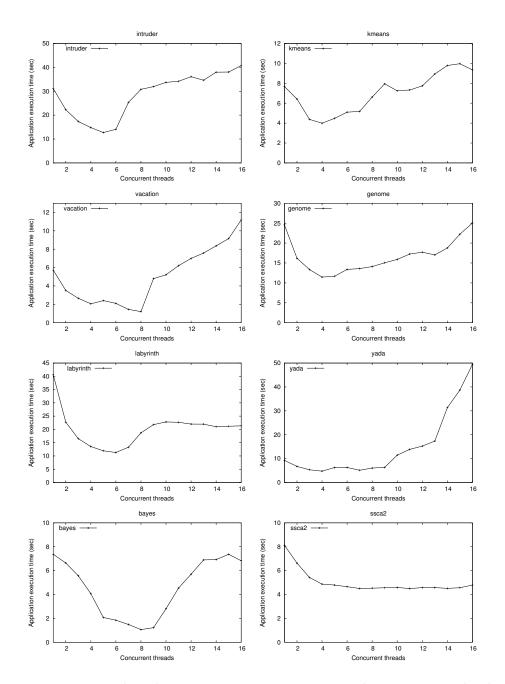

| 2.1 | Total application execution time varying the concurrency level $\ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

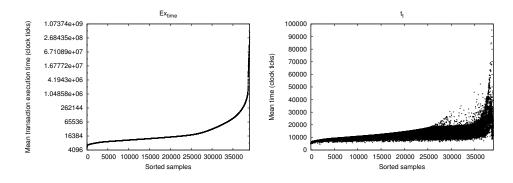

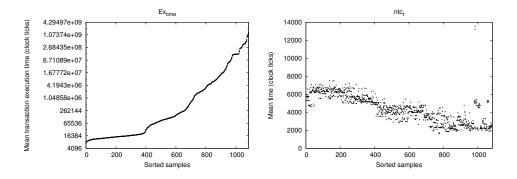

| 4.1 | Total mean execution time vs. mean execution time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51 |

| 4.2 | Total mean execution time vs. mean non-transactional time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51 |

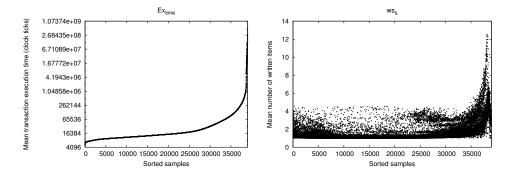

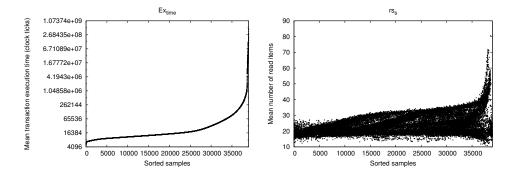

| 4.3 | Total mean execution time vs. mean read write set size $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52 |

| 4.4 | Total mean execution time vs. mean read set size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52 |

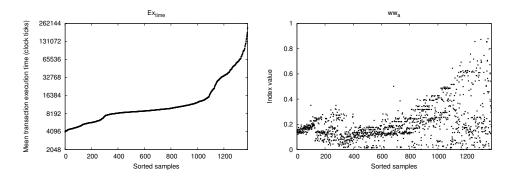

| 4.5 | Total mean execution time vs. write-write index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52 |

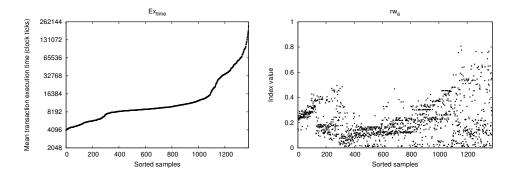

| 4.6 | Total mean execution time vs. read-write index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53 |

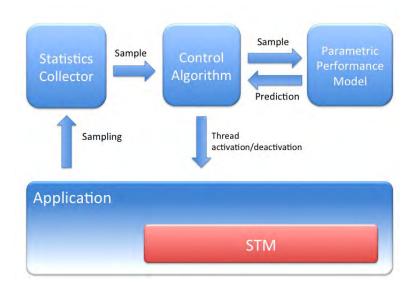

| 5.1 | System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58 |

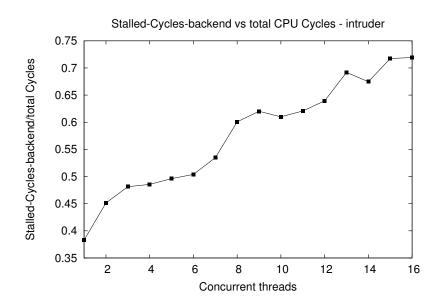

| 5.2 | Stalled cycles back-end for the intruder benchmark $\hdots \hdots \hdot$ | 61 |

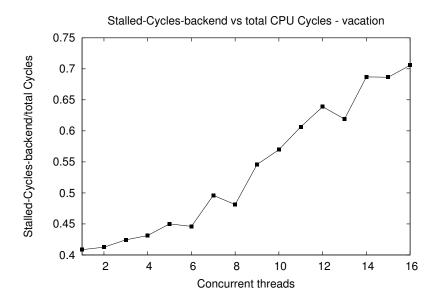

| 5.3 | Stalled cycles back-end for the vacation benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61 |

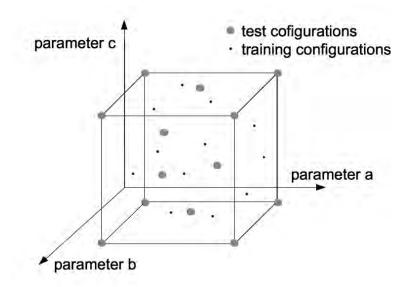

| 5.4 | Example training configurations and test configurations for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|     | case of three workload configuration parameters. $\ldots$ . $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66 |

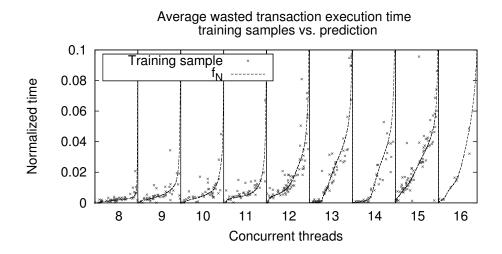

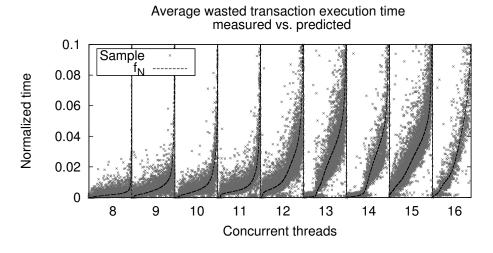

| 5.5 | Average wasted transaction execution time: training set vs. pre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | dicted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68 |

| 5.6 | Average wasted transaction execution time: measured vs. pre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|     | dicted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68 |

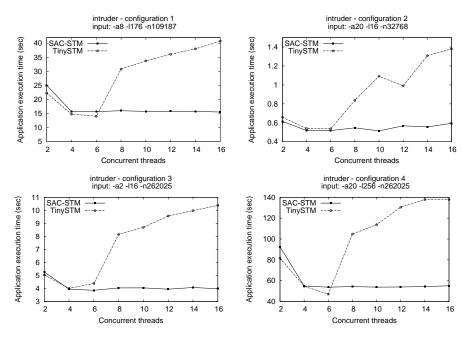

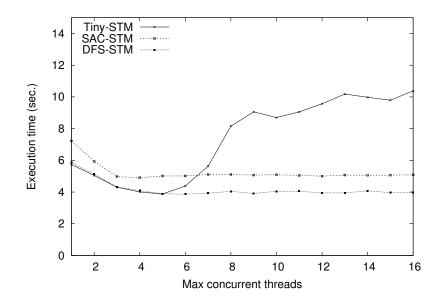

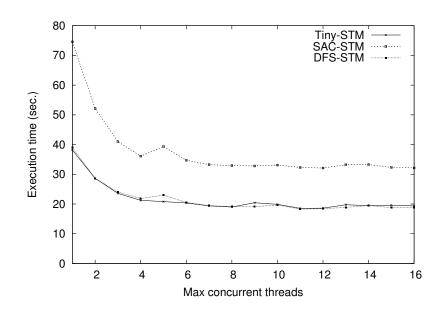

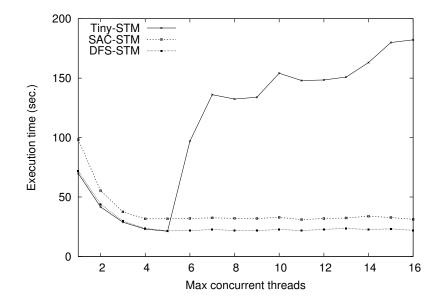

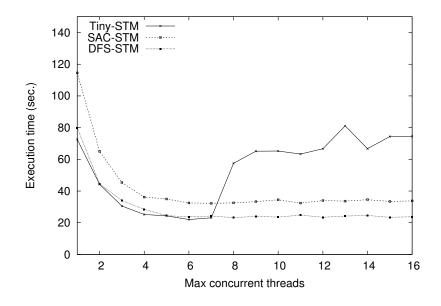

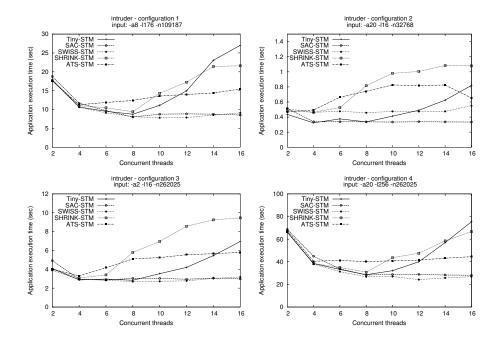

| 5.7  | Application execution time - intruder                               | 71  |

|------|---------------------------------------------------------------------|-----|

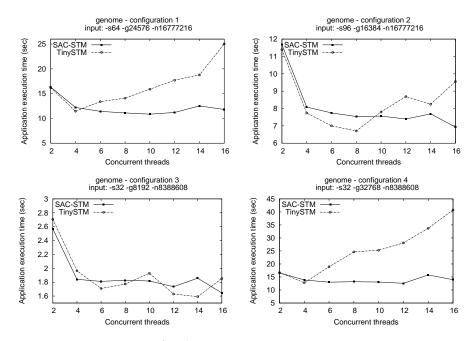

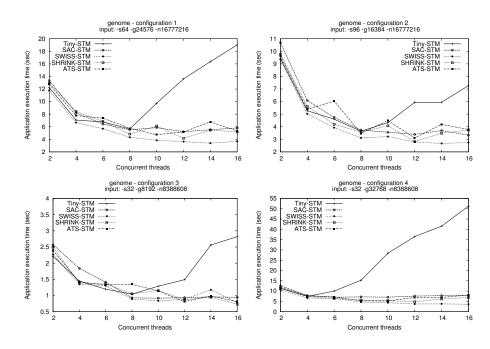

| 5.8  | Application execution time - genome                                 | 73  |

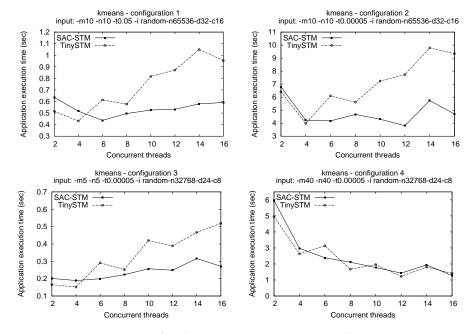

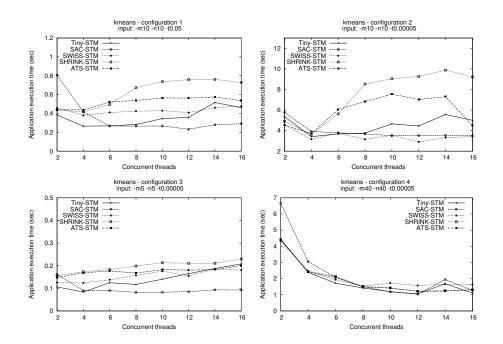

| 5.9  | Application execution time - kmeans                                 | 74  |

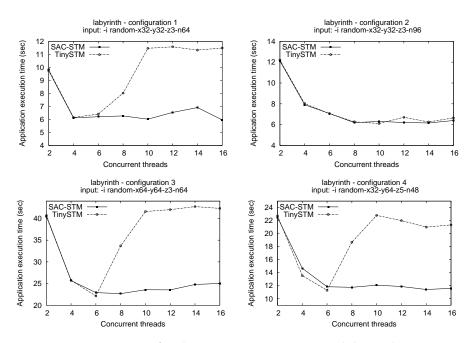

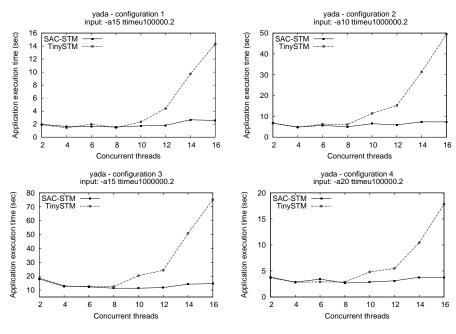

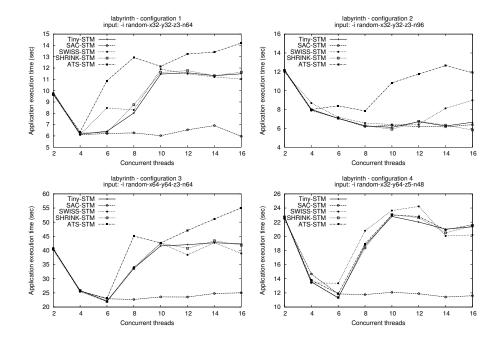

| 5.10 | Application execution time - labyrinth                              | 75  |

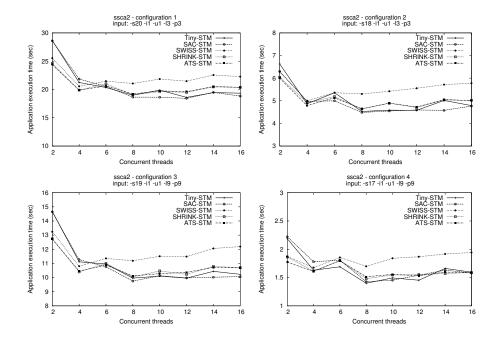

| 5.11 | Application execution time - ssca2                                  | 75  |

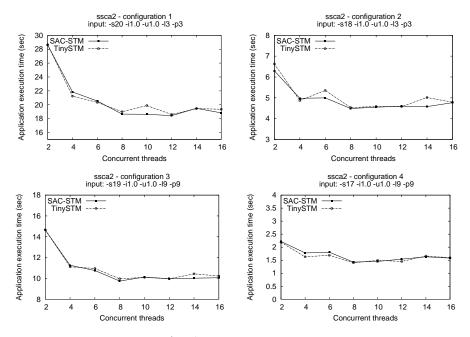

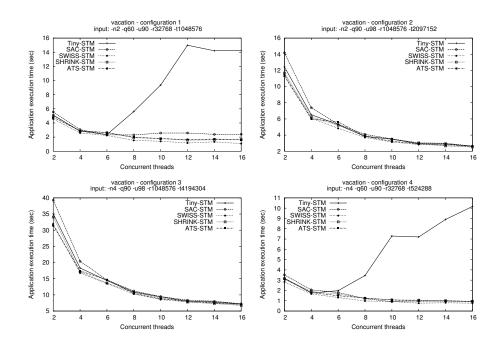

| 5.12 | Application execution time - vacation                               | 76  |

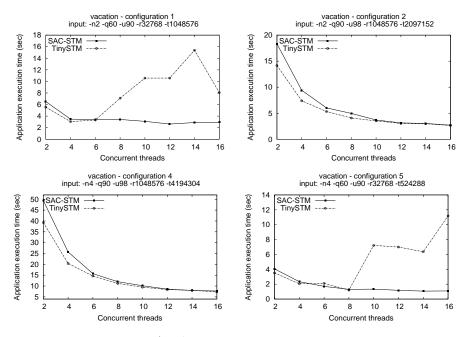

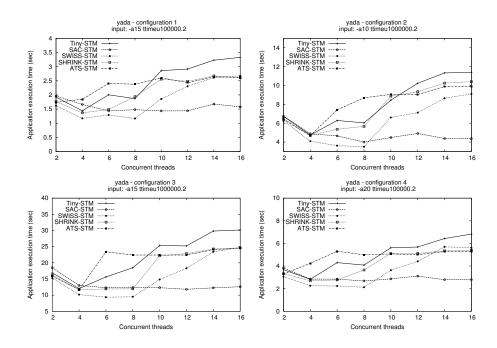

| 5.13 | Application execution - yada                                        | 77  |

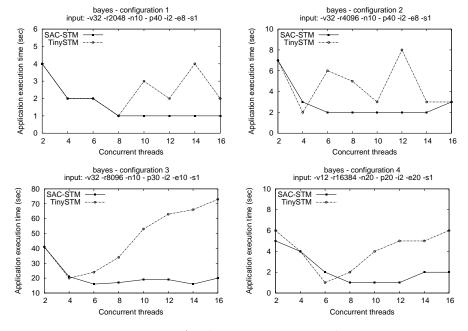

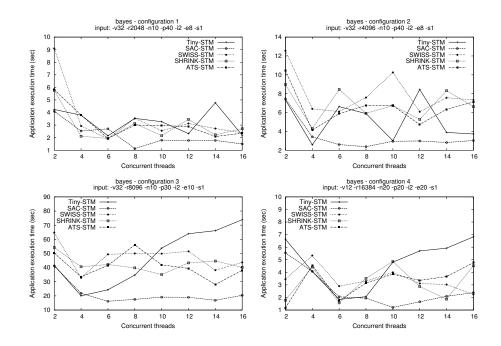

| 5.14 | Application execution - bayes                                       | 78  |

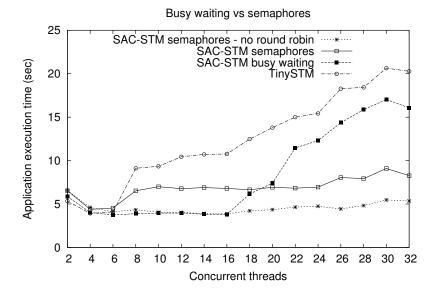

| 5.15 | Application execution time with intruder up to 32 threads. $\ldots$ | 80  |

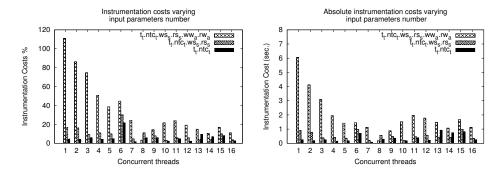

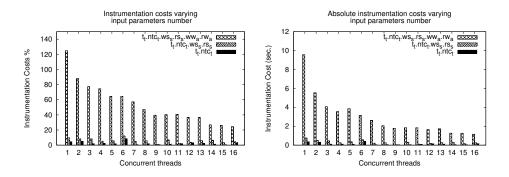

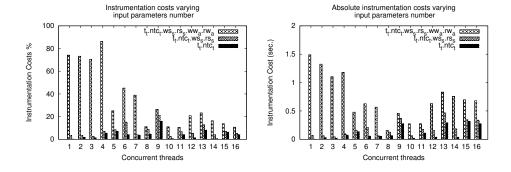

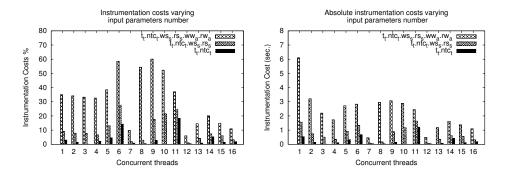

| 5.16 | Relative and absolute instrumentation costs - intruder              | 89  |

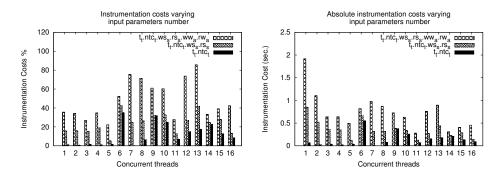

| 5.17 | Relative and absolute instrumentation costs - bayes                 | 90  |

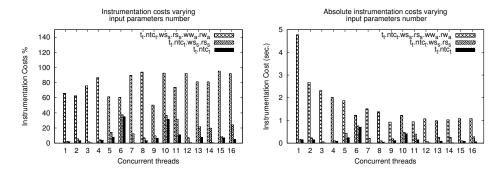

| 5.18 | Relative and absolute instrumentation costs - ssca2                 | 90  |

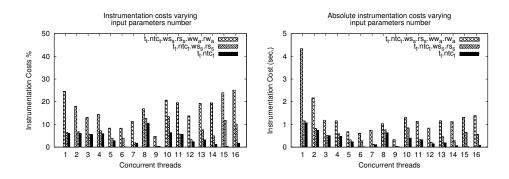

| 5.19 | Relative and absolute instrumentation costs - vacation              | 90  |

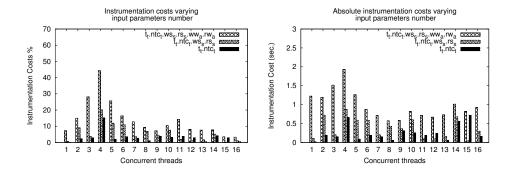

| 5.20 | Relative and absolute instrumentation costs - kmeans                | 91  |

| 5.21 | Relative and absolute instrumentation costs - labyrinth $\ldots$ .  | 91  |

| 5.22 | Relative and absolute instrumentation costs - yada $\hdots$         | 92  |

| 5.23 | Relative and absolute instrumentation costs - genome                | 93  |

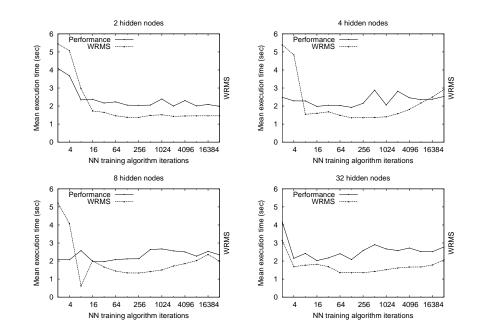

| 5.24 | Relation between the final achieved performance and WRMS for        |     |

|      | vacation                                                            | 95  |

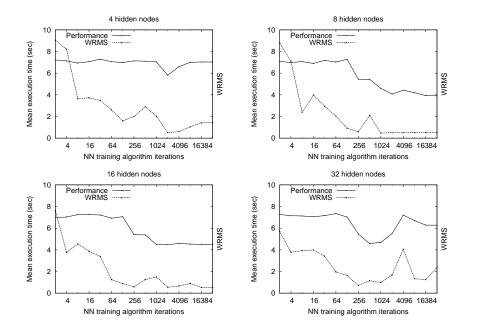

| 5.25 | Relation between the final achieved performance and WRMS for        |     |

|      | intruder                                                            | 96  |

| 5.26 | Extended SAC-STM architecture                                       | 98  |

| 5.27 | Results for intruder                                                | 100 |

| 5.28 | Results for ssca2                                                   | 101 |

| 5.29 | Results for vacation                                                | 102 |

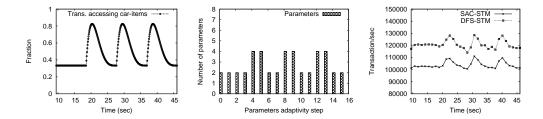

| 5.30 | Parameters and throughput variation over time for the modified                |     |

|------|-------------------------------------------------------------------------------|-----|

|      | vacation benchmark                                                            | 103 |

| 5.31 | Results for modified vacation                                                 | 104 |

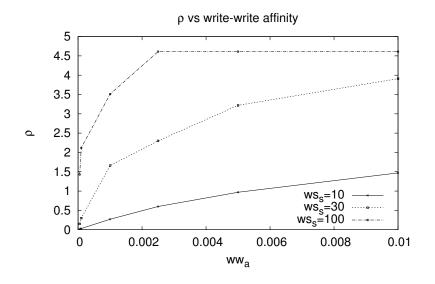

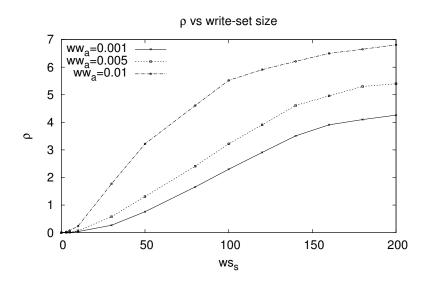

| 6.1  | Variation of $\rho$ with respect to the write-write affinity                  | 114 |

| 6.2  | Variation of $\rho$ with respect to the write-set size $\ldots \ldots \ldots$ | 114 |

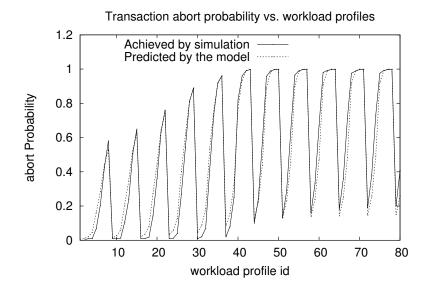

| 6.3  | Simulated vs predicted abort probability while varying $ww_a$ and             |     |

|      | $ws_s$                                                                        | 116 |

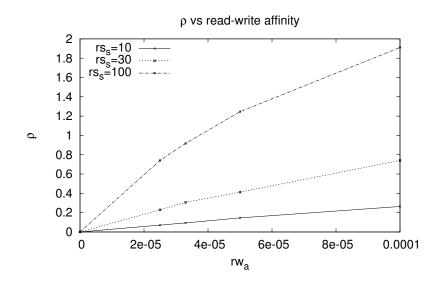

| 6.4  | Variation of $\rho$ with respect to the read-write affinity $\ldots \ldots$   | 117 |

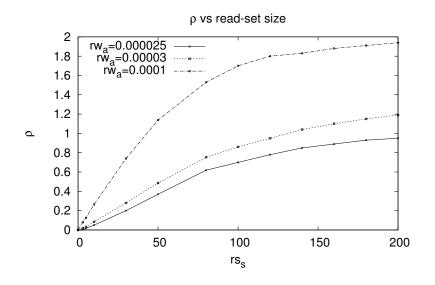

| 6.5  | Variation of $\rho$ with respect to the read-set size $\ldots \ldots \ldots$  | 118 |

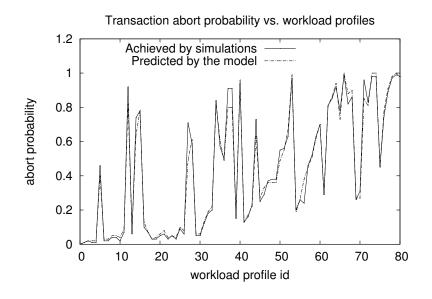

| 6.6  | Simulated vs predicted abort probability vs $rw_a,rs_s,ww_a,ws_s$ .           | 119 |

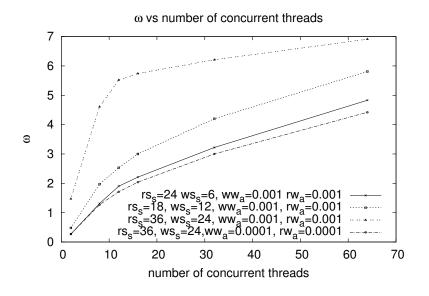

| 6.7  | Variation of $\omega$ vs the number of concurrent threads                     | 120 |

| 6.8  | Simulated vs predicted abort probability vs $k, rw_a, rs_s, ww_a, ws_s$       | 120 |

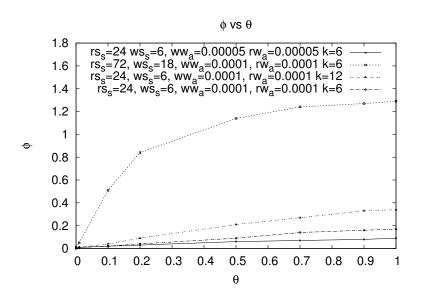

| 6.9  | Variation of $\phi$ with respect to $\theta$                                  | 121 |

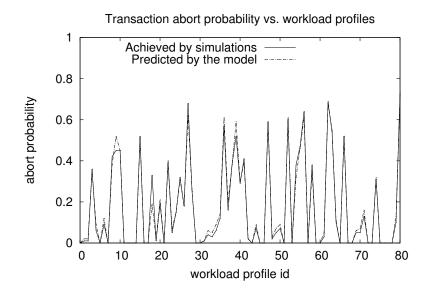

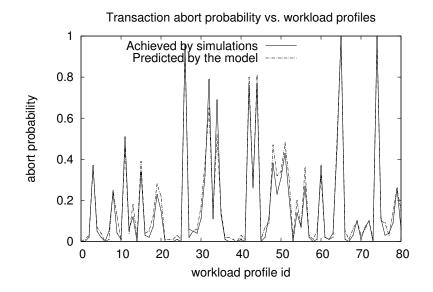

| 6.10 | Simulated vs predicted abort probability while varying all the                |     |

|      | workload profile parameters                                                   | 121 |

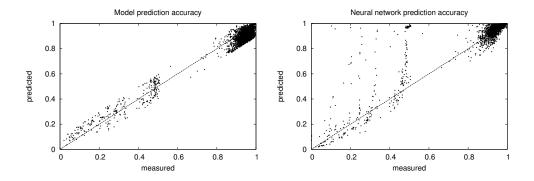

| 6.11 | Model and neural-network prediction accuracy $\ldots \ldots \ldots$           | 126 |

| 6.12 | CSR-STM architecture                                                          | 127 |

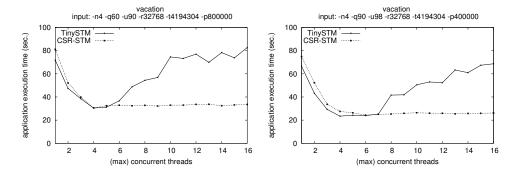

| 6.13 | Execution time for vacation with CSR-STM and TinySTM $~$                      | 131 |

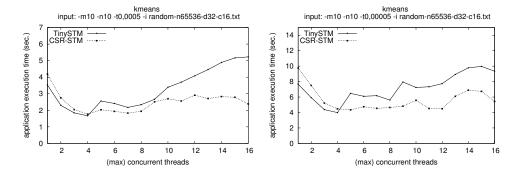

| 6.14 | Execution time for kmeans with CSR-STM and TinySTM                            | 132 |

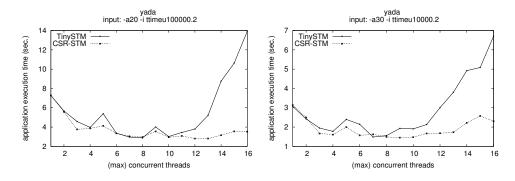

| 6.15 | Execution time for yada with CSR-STM and TinySTM $\ . \ . \ .$ .              | 132 |

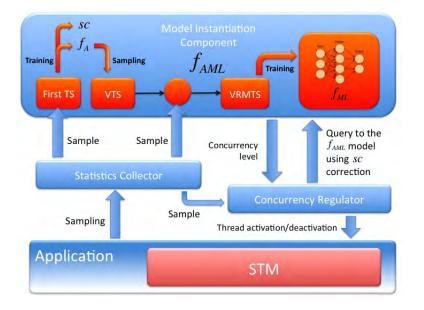

| 7.1  | System architecture                                                           | 146 |

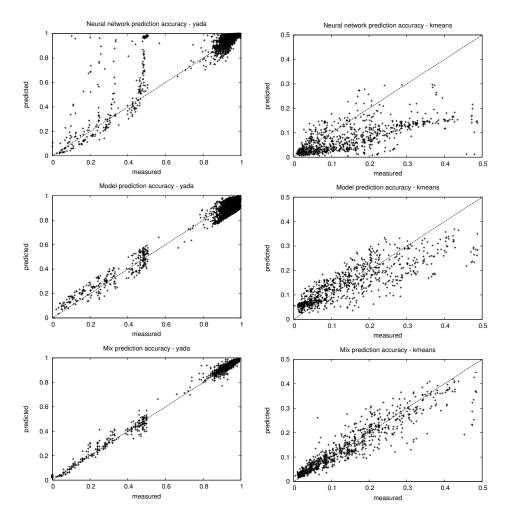

| 7.2  | Predictions accuracy - yada benchmark                                         | 153 |

| 7.3  | Predictions accuracy - kmeans benchmark                                       | 153 |

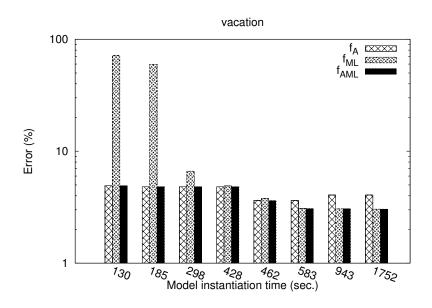

| 7.4  | Prediction error comparison - vacation                                        | 155 |

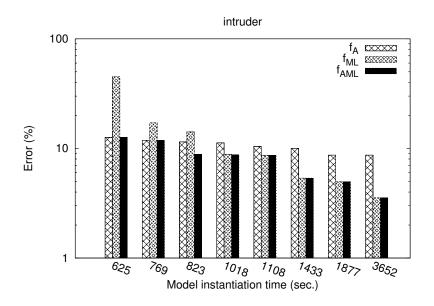

| 7.5  | Prediction error comparison - intruder                                        | 156 |

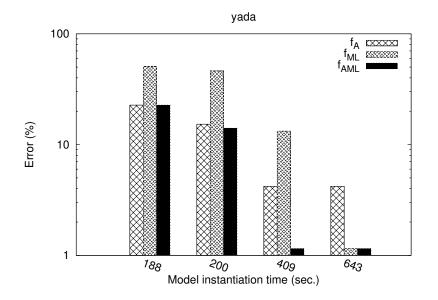

| 7.6  | Prediction error comparison - yada                                                |

|------|-----------------------------------------------------------------------------------|

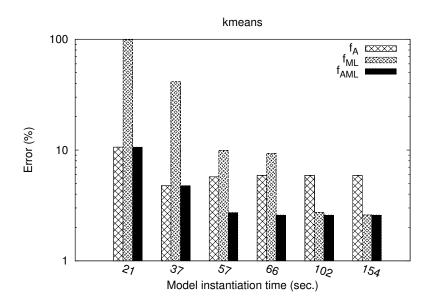

| 7.7  | Prediction error comparison - kmeans                                              |

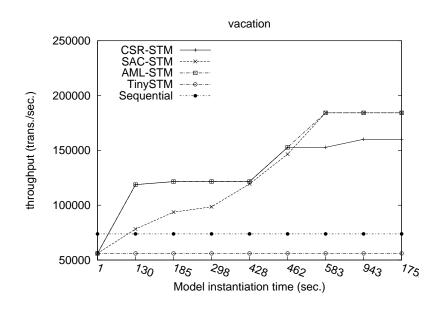

| 7.8  | Throughput - vacation                                                             |

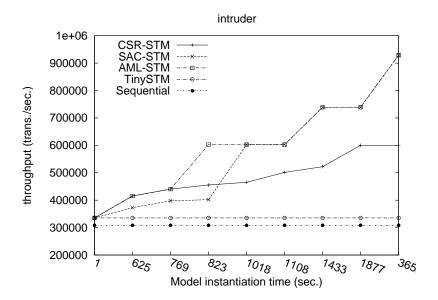

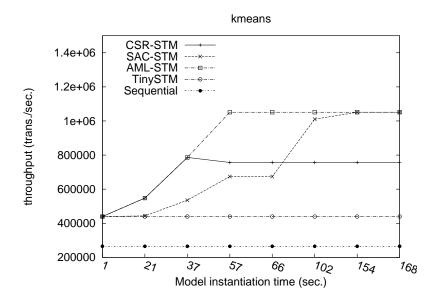

| 7.9  | Throughput - intruder                                                             |

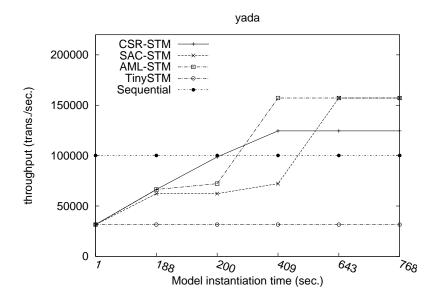

| 7.10 | Throughput - yada                                                                 |

| 7.11 | Throughput - kmeans                                                               |

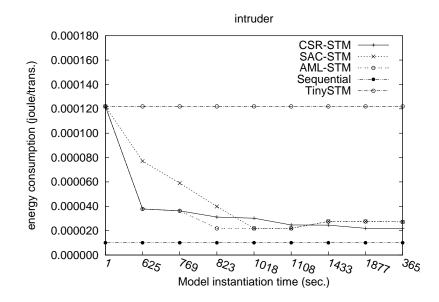

| 7.12 | Energy consumption per committed transaction - intruder 162                       |

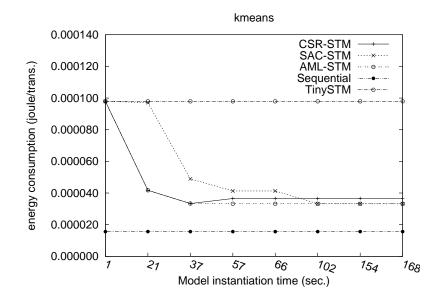

| 7.13 | Energy consumption per committed transaction - kmeans $\ldots$ 162                |

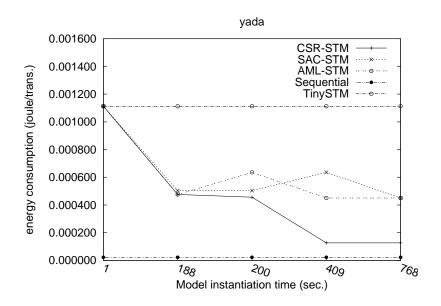

| 7.14 | Energy consumption per committed transaction - yada $163$                         |

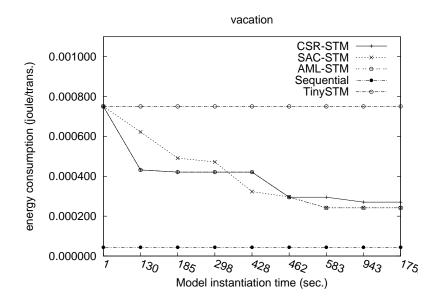

| 7.15 | Energy consumption per committed transaction - vacation $163$                     |

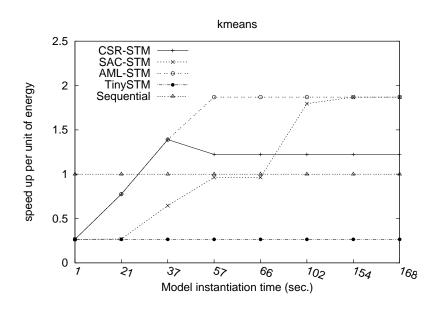

| 7.16 | Iso-energy speedup curves                                                         |

| 8.1  | Application execution time - intruder benchmark                                   |

| 8.2  | Application execution time - genome benchmark                                     |

| 8.3  | Application execution time - kmeans benchmark $\ldots \ldots \ldots \ldots 176$   |

| 8.4  | Application execution time - ssca2 benchmark                                      |

| 8.5  | Application execution time - vacation benchmark $\ldots \ldots \ldots \ldots 179$ |

| 8.6  | Application execution time - labyrinth benchmark $\ldots \ldots \ldots 180$       |

| 8.7  | Application execution time - yada benchmark                                       |

| 8.8  | Application execution time - bayes benchmark                                      |

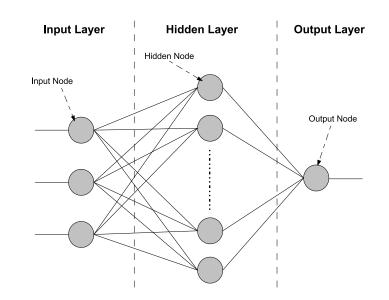

| A.1  | Example of a three layer fully connected neural network 193                       |

# List of Tables

| 5.1 | Input features correlation for the applications with the STAMP |

|-----|----------------------------------------------------------------|

|     | benchmark suite                                                |

| 5.2 | Input features variance for the applications with the STAMP    |

|     | benchmark suite                                                |

| 5.3 | Parameters configuration for the performance tests 99          |

| 5.4 | Minimum achieved percentage of ideal speedup 105               |

|     |                                                                |

| 6.1 | Abort probability prediction error (and its variance) 125      |

| 7.1 | Average error and variance comparison                          |

|     |                                                                |

| B.1 | Qualitative summary of STAMP application's runtime transac-    |

|     | tional characteristics                                         |

## Acknowledgements

My first special thanks goes to my colleagues and friends Pierangelo Di Sanzo and Alessandro Pellegrini.

Thanks Piero because without your help probably I'd still be looking for a good research topic for my Phd, because without your being stubborn many of the our papers would not be accepted and because you always find the right moment to say "sta chiudendo!".

Thanks Alessandro because without your help probably I'd still be trying to remove some "segmentation fault" error from my code, because you provided to me the right psychological support during my first important international conference in Washington D.C. and because you have been my official cigarettes provider.

A special thanks to my advisor and leader of our research group Prof. Bruno Ciciani, who is more than just a great scientist, but a master of life. He is like a father for all the guys of our research group and he transmitted to us the enthusiasm for the teaching. He taught me not only the approach to scientific research but to be a honest person and to never compromise myself for any reason.

A special thanks to Prof. Francesco Quaglia, that I consider like a second

advisor. I met him some years ago, when I was a student of bachelor degree, and I immediately perceived the reliability and the competence that distinguish him. During the last years he gave to me the right suggestions to solve the problems that manifested during my doctorate and he taught to me that the quality of the work is the only target that must be addressed. He is a special person, despite some serious personal problems he has always found the time to work with us. Thank you very much Francesco and always "Forza Roma"!

Together with Bruno and Francesco, a special thanks goes to Prof. Paolo Romano. He was my advisor for the master degree thesis and he gave me the opportunity to have a wonderful research experience in Lisbon. He has been a reference point for his way to approach and solve the problems. Paolo please say thank you to Anna for the wonderful stuffed squid she coked for us when I was in Lisbon!

I am also grateful to Prof. Vincent Gramoli and Prof. Jean-François Méhaut for having accepted to serve as external referees of this dissertation, and to Prof. Giorgio Grisetti for having served as second member of my thesis committee.

A special thanks to the young researchers who have been close to me in any situation (Roberto Vitali, Roberto Palmieri and Sebastiano Peluso): their jokes and laughters greatly alleviated the stress experienced during the whole PhD program.

A loving thanks to my family (Rosa, Renzo and Simone), the only reason that made it possible to achieve this result. They dedicated their entire life to me and my brother. I wish I knew some way of returning even a fraction of what they have given me.

A final thanks to all the people that gave and thought to me something important, for my work and for my life: Valeria Cruciani, Andrea "Pasticca" Bassignani, Emiliano "Pera" Di Giambattista, Fabio "Francis" Francescangeli, Alessia Iacuitto, Sara Cherubini, Daniele "Dang" D'angeli, Lucio D'Angeli, Riccardo "Ninetto" Colantoni, Veronica Cavalli, Luca Pascasi, Federico "Generale" Boni, Andrea "Zione" Capata, Cristina Canu, Tatiana Lopez, Leonardo "Mister" Bevilacqua, Sabrina D'auria, Marco "Il Mentore" Martini and Francesca Casciola.

Rome, Italy March 31th, 2014

Diego

## Abstract

Software Transactional Memory (STM) has emerged as a powerful programming paradigm for concurrent applications. It allows encapsulating the access to data shared across concurrent threads within transactions, thus avoiding the need for synchronization mechanisms to be explicitly coded by the programmer. On the other hand, synchronization transparency must not come the expense of performance. Hence, STM-based systems must be enriched with mechanisms providing optimized run-time efficiency. Among the issues to be tackled, a core one is related to determining the optimal level of concurrency (number of threads) to be employed for running the application on top of the STM layer. For too low levels of concurrency, parallelism can be hampered. On the other hand, overdimensioning the concurrency level may give rise to thrashing phenomena caused by excessive data contention and consequent transaction aborts.

In this thesis we propose a set of techniques in order to build "application specific" performance models allowing to dynamically tune the level of concurrency to the best suited value depending of the specific execution phase of the application. We will present three different approaches: a) one based on a pure Machine Learning (ML) model that doesn't require a detailed knowledge of the application internals to predict the optimal concurrency level, b) one based on a parametric analytical performance model customized for a specific application/platform through regression analysis that, respect to the previous one, requires a lighter training phase and c) one based on a combination of analytical and Machine Learning techniques, that allows to combine the strengths of the previous two approaches, that is it has the advantage of reducing the training time of pure machine learning methods avoiding the approximation errors typically affecting pure analytical approaches. Hence it allows very fast construction of highly reliable performance models, which can be promptly and effectively exploited for optimizing actual application runs.

We also present real implementations of concurrency regulation architectures, based on our performance predictions approaches, which have been integrated within the open source TinySTM package, together with experimental data related to runs of application profiles taken from the STAMP benchmark suite demonstrating the effectiveness of our proposals. The experimental data confirm how our self-adjusting concurrency schemes constantly provides optimal performance, thus avoiding performance loss phases caused by non-suited selection of the amount of concurrent threads and associated with the above depicted phenomena.

Moreover we present a mechanism that allows to dynamically shrinks or enlarges the set of input features to be exploited by the performance predictors. This allows for tuning the concurrency level while also minimizing the overhead for input-features sampling, given that the cardinality of the input-feature set is always tuned to the minimum value that still guarantees reliability of workload characterization. We also present a fully fledged implementation of this solution again within the TinySTM open source framework, and we provide the results

$\mathbf{2}$

of an experimental study relying on the STAMP benchmark suite, which show significant reduction of the application execution time with respect to proposals based on static feature selection.

### Publications

Most of the material provided by this dissertation has been presented in (or has contributed to the production of) the following technical articles I have coauthored:

- Diego Rughetti, Pierangelo Di Sanzo, Bruno Ciciani, Francesco Quaglia Analytical/ML Mixed Approach for Concurrency Regulation in Software Transactional Memory. *Proceedings of the 14th IEEE/ACM International* Symposium on Cluster, Cloud and Grid Computing, (CCGrid). IEEE/ACM Chicago, IL, USA May 26-29, 2014

- 2 Diego Rughetti, Perangelo Di Sanzo, Bruno Ciciani, Francesco Quaglia. Machine Learning-based Self-adjusting Concurrency in Software Transactional Memory Systems. Proceedings of the 20th IEEE International Symposium On Modeling, Analysis and Simulation of Computer and Telecommunication Systems, (MASCOTS). pages 278-285, IEEE Computer Society, August 2012, Arlington, VA, USA

- 3 Pierangelo Di Sanzo, Francesco Del Re, Diego Rughetti, Bruno Ciciani and Francesco Quaglia Regulating Concurrency in Software Transactional Memory: An Effective Model-based Approach. Proceedings of the 7th IEEE International Conference on Self-Adaptive and Self-Organizing Systems, (SASO). IEEE Computer Society, September 2013, Philadelphia, USA

- 4 Diego Rughetti, Pierangelo Di Sanzo, Bruno Ciciani, Francesco Quaglia Dynamic Feature Selection for Machine-Learning Based Concurrency Regulation in STM. Proceedings of the 22st Euromicro International Conference on Parallel, Distributed and Network-Based Processing, PDP Euromicro, University of Turin, Turin, Italy, February 2014

- 5 Diego Rughetti, Pierangelo Di Sanzo and Alessandro Pellegrini Adaptive Transactional Memories: Performance and Energy Consumption Tradeoffs. Proceedings of the 3rd IEEE Symposium on Network Cloud Computing and Applications, (NCCA). IEEE Computer Society, February 2014, Rome, Italy

The techniques presented in this dissertation have been used also in context different from Software Transactional Memory (e.g. Hardware Transactional Memory and Data Grid platforms deployed in Cloud Computing environments) bringing to the production of the following technical articles I have coauthored:

- Diego Rughetti, Paolo Romano, Francesco Quaglia, Bruno Ciciani. Autonomic Tuning of the Parallelism Degree in Hardware Transactional Memory. SUBMITTED to the 20th International European Conference on Parallel Processing, (Euro-Par). Springer, August 2014, Porto, Portugal

- 2 Pierangelo Di Sanzo, Francesco Maria Molfese, Diego Rughetti, Bruno Ciciani Providing Transaction Class-Based QoS in in-Memory Data Grids Via Machine Learning. Proceedings of the 3rd IEEE Symposium on Network Cloud Computing and Applications, (NCCA). IEEE Computer Society, February 2014, Rome, Italy

- 3 Perangelo Di Sanzo, Diego Rughetti, Bruno Ciciani, Francesco Quaglia. Auto-tuning of Cloud-based In-memory Transactional Data Grids via Ma-

4

chine Learning. Proceedings of the 2nd IEEE Symposium on Network Cloud Computing and Applications, (NCCA). IEEE Computer Society, December 2012, London, UK

- 4 Perangelo Di Sanzo, Francesco Antonacci, Bruno Ciciani, Roberto Palmieri, Alessandro Pellegrini, Sebastiano Peluso, Francesco Quaglia, Diego Rughetti, Roberto Vitali. A Framework for High Performance Simulation of Transactional Data Grid Platforms. *Proceedings of the 6th ICST Conference of Simulation Tools and Techniques*, (SIMUTools). ICST, March 2013, Nice, France

- 5 Paolo Romano, Diego Rughetti, Bruno Ciciani, Francesco Quaglia. APART: Low Cost Active Replication for Multi-tier Data Acquisition Systems. Proceedings of the 7th IEEE International Symposium on Network Computing and Applications, (NCA). IEEE Computer Society, July 2008, Cambridge, MA, USA, Winner of the Best Paper Award

## Chapter 1 Introduction

Software Transactional Memory (STM) [1] is an attractive programming paradigm for parallel/concurrent applications. Particularly, by relying on the notion of atomic transaction, STM stands as a friendly alternative to traditional lockbased synchronization. More in detail, code blocks accessing shared-data can be marked as transactions, thus demanding coherency of data access/manipulation to the STM layer, rather than to any handcrafted synchronization scheme provided by the programmer. The relevance of the STM paradigm has significantly grown given that multi-core systems have become mainstream platforms, so that even entry-level desktop and laptop machines are nowadays equipped with multiple processors and/or CPU-cores. Also, transaction is the representative technology for several in-memory Cloud-suited data-platforms (such as Red Hat's Infinispan, VMware vFabric GemFire [2], Oracle Coherence [3] and Apache Cassandra [4]), where the encapsulation of application code within transactions allows concurrent manipulation of in-memory kept application data according to specific isolation levels, which is done transparently to the programmer.

Even though the STM potential for simplifying the software development process is extremely high, another aspect that is central for the success, and the further diffusion of the STM paradigm relates to the actual level of performance it can deliver. As for this aspect, one core issue to cope with in STM is related to exploiting parallelism while also avoiding thrashing phenomena due to excessive transaction rollbacks, caused by excessive contention on logical resources, namely concurrently accessed data portions. We note that this aspect has reflections also on the side of resource provisioning in the Cloud, and associated costs, since thrashing leads to suboptimal usage of resources (including energy) by, e.g., PaaS providers offering STM based platforms to customers. One such platform has been recently presented by the Cloud-TM project [5], and is aimed at simplifying and optimizing the process of deploying data centric applications in the Cloud.

In order to deal with the run-time efficiency issue in STM, literature approaches can be framed within different sets of orthogonal solutions. On one side can we find optimized schemes for transaction conflict detection and management [6, 7, 8, 9, 10, 11]. These include proposals aimed at dynamically determining which threads need to execute specific transactions, so to allow transactions to be expected to access the same data to run along a same thread in order to sequentialize and spare them from incurring the risk of being aborted with high probability. Other proposals rely instead on pro-active transaction scheduling [12, 13] where the reduction of performance degradation due to transaction aborts is achieved by avoiding to schedule (hence delaying) the execution of transactions whose associated conflict probability is estimated to be high. All the above schemes are not meant to optimize the concurrency level (that is the number of threads) to be used for running the application, thus they generally operate on top of configurations where the number of threads is predetermined at application startup.

On the other side we find solutions aimed at supporting performance optimization via the determination of the best suited level of concurrency to be exploited for running the application on top of the STM layer (see, e.g., [14, 15, 16]). These solutions are clearly orthogonal to the aforementioned ones, being potentially usable in combination with them. We can further distinguish these approaches depending on whether they can cope with dynamic or static application execution profiles, and on the type of methodology that is used to determine (predict) the well suited level of concurrency for a specific (phase of the execution of the) application. Approaches coping with static workload profiles are not able to predict the optimal level of concurrency for applications where classical parameters expressing proper dynamics of the applications (such as the average number of data-objects touched by a transactional code bock) can vary over time. For those scenarios approaches coping with dynamic workload profiles usually allows to obtain better prediction performance.

The prediction approaches that have been proposed in literature either rely on analytical methods, or on black-box Machine Learning (ML) methodologies. The first ones have the advantage of generally requiring a lightweight application profiling for gathering data to be filled to the prediction model, but provide (slightly) less accurate predictions and in some cases require stringent assumptions to be met by the real STM system in order for its dynamics to be reliably captured by the analytical formulas (see, e.g., [17]). On the contrary, ML methods usually require much expensive profiling in order to build the knowledge base that would suffice to instantiate the performance prediction model, which may make the actuation of the optimized concurrency configuration untimely. On the other hand, they typically allow high precise estimation of the real performance trends of the STM system as a function of differentiated parameters

9

(see, e.g., [18]).

In this thesis we cope with the issue of determining the optimal level of concurrency by presenting a suite of techniques for dynamic concurrency regulation based on Machine learning, on analytical modelling and on an hybrid technique that mixes the previous two approaches allowing to chase the best of the two methodologies by tackling the shortcomings intrinsic in each of them. The approaches we provide are able to cope with cases where the actual execution profile of the application, namely the workload features, can change over time, such as when the (average) size of the data-set accessed by the transactional code in read or write mode changes over time (e.g. according to a phase-behavior). This is not always allowed by pure analytical approaches [14, 16]. Furthermore, as we will show later in this thesis, our hybrid approach represents a methodology for very fast construction of a highly reliable performance model allowing the determination of the optimal level of concurrency for the specific STM-based application. This is relevant in generic contexts also including the Cloud, where the need for deploying new applications (or applications with reshuffling in their execution profile), while also promptly determining the system configurations allowing optimized resource usage, is very common.

During the development of our concurrency regulation techniques we verified that one drawback of the ones that use Machine Learning is related to the need for constantly monitoring the set of selected input features to be exploited by the machine learner. This may give rise to non-minimal overhead, especially when considering that STM applications may exhibit fine-grain transactions, natively requiring a (very) reduced amount of CPU cycles for finalizing their task. To cope with this issue, we developed a solution where the set of input features exploited by the machine learning based performance model is dynamically shrunk. In other terms, the complexity of both the workload characterization model and the associated performance model is (dynamically) reduced to the minimum that still guarantees reliable performance prediction. This leads to reducing the amount of feature samples to be taken for performance prediction along any wall-clock-time window, hence reducing the actual overhead for performance prediction.

Together with the aforementioned approaches, we also present three real implementations of concurrency regulation architectures, integrated with the TinySTM open source package [19], which exploit the developed models to dynamically tune the number of threads to be used for running the application. Further, we report experimental results, achieved by running the applications belonging to the STAMP benchmark suite [20] on top of a 16-core HP ProLiant machine, which show the effectiveness of the proposed approaches.

The reminder of the thesis is organized as follows. In Chapter 2 a description of software transactional memories and of the concurrency regulation problem in STM based applications is provided. The state of art about performance optimization in STM is discussed in Chapter 3. In Chapter 4 the models for the target STM applications and for the transactional workload are presented. In Chapters 5, 6, 7 three innovative approaches for autonomic concurrency regulation based respectively on machine learning, analytical modelling and a mix of the previous two are presented and discussed. We conclude the thesis presenting in Chapter 8 a detailed comparison between the performance reachable using different standard and adaptive STM implementations.

To help the reader to better understand the insights of the approach presented in Chapter 5 we provide in Appendix A a recall of the used machine learning technique. Moreover a brief overview of the STAMP benchmark suite,

11

the most commonly used testbed for STM platforms, is provided in Appendix B.

# CHAPTER 2 Software Transactional Memories

#### 2.1 Software Transactional Memories brief overview

Software transactional memories (STMs) [1] are a high attractive programming paradigm for parallel applications. The first proposals about Transactional Memories (TMs) [8] were dated back to 90s but research on this topic gained momentum since 2004, when the multi-core processors became available for commercial market. Proliferation of multi-core architectures allowed parallel programming to exit from the niche of high-performance and scientific computing and turned it into a mainstream concern for software industry. One of the main challenge of parallel programming is the synchronization of concurrent accesses to shared memory by multiple, concurrent threads. A traditional technique is the one based on locks, but it has well-known pitfalls: sophisticated fine-grained locking can bring to the risk of deadlocks and data races while more simple coarse-grained locking can bring to scalability limitations. Moreover scalable libraries that use fine-grained lock cannot be easily mixed in a way that preserve scalability and avoid data races and deadlock [21]. STMs inherit the transaction based approach typical of Database systems (DBS), bringing it into the world of parallel programming. They free the programmers from the responsibility of design and verify complex fine-grained lock synchronization schemes. By avoiding deadlocks and automatically allowing fine-grained concurrency, transactional language constructs enable the programmer to compose scalable applications safely out of thread-safe libraries. As in SQL programming, with STM the programmers just have to mark code blocks which have to be executed as atomic transactions. Then the underling STM layer takes care of all the synchronization issues providing the illusion that transactions are executed serially. So the programmers can reason serially about the correctness of their applications. The STM layer, of course, doesn't execute the transactions serially. Actually, hiding all synchronization issues to the application, it allows multiple transactions to execute concurrently by relying on a Concurrency Control Protocol (CCP).

We stated that Transactional Memories are inspired to transactional DBS, but between them exists some basic differences [22]. The execution of in memory transaction ensures atomicity, isolation and consistency. Durability instead is not ensured because all the read and write operations are executed only in volatile memory. This brings to another significant difference: the execution time is usually smaller compared to database transactions because the access to persistent storage during data update is not necessary. Moreover in memory transactions don't pay the cost of the overheads for SQL parsing and plan optimization that characterize database environments. This differences allow STMs to ensure transactions execution times usually two or three orders of magnitude smaller than in conventional database environments [23, 24]. Another difference between STM and DBS is related to the isolation level required for memory transactions. For DBS serializability is considered largely sufficient, but this level of isolation allows transactions that will be subsequently aborted to read inconsistent data. In [25] the authors show that the effects of observing inconsistent states can have much more negative side effects in STMs that in DBS. In fact in STMs transactions can be used to manipulate program variables that directly affect the execution flow of user applications so, due to the observation of arbitrarily inconsistent memory states could bring the application to stall in infinite loops or in exceptions that may never occur in any sequential execution. Instead for DBS transactions are executed via interfaces with defined and more restricted semantic (e.g. SQL interfaces) and are executed in a "bulletproof" component, the database management system (DBMS), designed to avoid crashes or hangs in the case the transactions observe inconsistent data. For these reasons in memory transactions [26] require an isolation level called opacity, higher than serializability, that in addition prevents all transactions (also transactions that will be subsequently aborted) from seeing inconsistent values of data items. Today research on STMs topics is very active. Commercial releases of STMs do not exist yet but many research prototype (e.g [6, 19, 27, 28]) and prototype for commercial systems (e.g. [29]) are available. Moreover Intel recently released a processor with Transactional Synchronization Extensions [30] that represents the first (low cost) commercial implementation of hardware transactional memory.

#### 2.2 The problem of concurrency in STM

One of the main challenge that a programmer have to face when designing parallel and distributed application is scalability, that is the ability of an application to proportionally increase its performance when the amount of available computing resources is increased. Focusing our attention on centralized multi-core systems, an ideal parallel application should scale linearly with the number of available core. Usually this level of scalability is not reachable due to two main factors:

- contention on physical resource,

- contention on logical resource.

Whit physical resource contention we denote the contention experienced by processes/threads that compose the parallel application when they try to access shared hardware resource (e.g. memory buses). It is strictly related to the specific platform used to run the application and keeping under control its side effect on performance require a detailed knowledge of the hardware. With logical resource contention we denote the contention experienced by the threads that compose the parallel application when they try to concurrently access shared logical resources (e.g. data in main memory). It is strictly related to the application logic and usually its side effects on application performance are higher than the ones due to physical contention: it brings to an higher performance degradation and it limits the scalability more than physical contention that can become negligible. To limit the impact of logical contention on scalability and performance the programmer must have a detailed knowledge of the application logic and of the application data access pattern. In this way the programmer can:

• divide properly the work between threads: the programmer should try to divide the work in a way that the needed synchronization between process/thread is minimum; • when synchronization between thread/process is not avoidable: the programmer should use synchronization mechanism that minimizes wasted time.

But as we explained in paragraph 2.1, in the context of centralized transactional applications, these tasks are not trivial and STM helps to simplify developer's work taking care of synchronization of access to shared data. This implies that the logical contention experimented by the transactional application is closely related to the conflict detection mechanism implemented inside the STM. More in detail the performance of STM based application depends essentially on three factors:

- the specific transactional application workload,

- the conflict detection and contention management mechanisms implemented inside the STM,

- the level of parallelism used to execute the application.

About transactional application workload, two of the main parameters that can characterize a transactional workload are:

- the ratio between read and write on shared data,

- the distributions of read and write operation on shared data.

Workload with an high shared read/shared write ratio can be defined read intensive. Given an enough big fixed dataset, this type of workload, if the read and write operations are not concentrated on few shared data, usually brings to a low logical contention having, in this case, a little impact on application performance. Workload with low shared read/shared write ratio can be defined write intensive. In this case, especially if the read and write operations are concentrated on few shared data, the logical contention is high and has a significant impact on application performance. Between these two extremes, the logical contention can vary proportionally as a function of the ratio between shared read/shared write ratio and the shared data access distribution.

The conflict detection mechanism determines the point at which an inconsistency in the shared object is detected. Different design choices can have a substantial impact on the performance of an STM platform and on the degree to which it is suited to different kinds of workload. So it is necessary to find the right trade-off between the design choices that avoid wasted work (due to transaction abort) and the ones that avoid concurrency loss (where a transaction is stalled or aborted, even though it would eventually commit). Three main conflict detection mechanism families can be defined:

- *eager*: also called pessimistic, with this type of policy a conflict is detected as soon as it arises, aborting transaction immediately without waiting for the commit stage;

- *lazy*: also called optimistic, with this type of policy a conflict is detected at commit time, so the transaction is executed until it reaches the commit and then eventually aborted;

- *mixed*: this policy is a mix of the previous ones, it detects write-write conflicts early (since at most one of the conflicting transactions can ever commit) and it detects read-write conflicts late (since both may commit if the reader does so first).

In [31] a performance comparison using experimental evaluation of benchmarks between eager and lazy conflict detections have been presented. The results shows that in those applications where threads share a small number of data, the lazy policies are faster than the eager ones, while the latter are better in applications where threads share several data among themselves. This result brings to the conclusion that no single policy is superior across all kinds of workloads.

A Contention Manager(CM) that implements one or more contention resolution policies can be used to mitigate the side effect on performance due to conflicts between transactions. When a conflict is detected the actions taken by the CM to resolve it depend on the specific implemented resolution policy that can select whether:

- to abort the transaction  $t_1$  that detects the conflict or

- to abort the opponent transaction  $t_2$  that it encounters or

- to delay or not either transactions.

A lot of different contention management policies have been developed [32, 33]:

- *Passive*:  $t_1$  aborts and re-executes

- Aggressive: each opponent transaction  $t_2$  is immediately aborted

- Polite: for a fixed number N of exponentially growing interval of time, t<sub>1</sub> waits that the opposite transaction t<sub>2</sub> commits. At the end of each interval t<sub>1</sub> checks if the conflicting transaction has finished with the data. If the check fails for all the N intervals than the opposite transaction t<sub>2</sub> is aborted.

- *Karma*: this is a priority based policy in which an acquiring transaction immediately aborts other conflicting transactions with lower priority. If

the acquiring transaction  $t_1$  has lower priority it wait trying to acquire the access to the data for N times, where N is the difference between the priority of the conflicting transactions. If the opponent transaction  $t_2$  has not completed after all the N iterations, it is aborted. The priority of each transaction is established on the basis of the number of data accessed by the transaction.

- *Eruption*: this policy is similar to Karma but it adds the blocked transaction's priority to the active transaction's priority.

- Greedy: Each transaction obtains a timestamp when it starts the first time. If a conflict occurs  $t_1$  aborts  $t_2$  only if the timestamp associated to  $t_2$  is higher to the ones associated to  $t_1$  or if  $t_2$  is waiting. Otherwise  $t_1$ starts waiting for  $t_2$  indefinitely.

- *Kindergarten*: in this policy a transaction  $t_1$  is aborted each time that it conflicts for the first time with another transaction  $t_2$ . If  $t_1$  conflict again, one or more time, with  $t_2$ , then  $t_2$  is aborted.