# Cross-State Events: a New Approach to Parallel Discrete Event Simulation and its Speculative Runtime Support

Alessandro Pellegrini<sup>a</sup>, Francesco Quaglia<sup>b,\*</sup>

<sup>a</sup>DIAG, Sapienza, University of Rome, Via Ariosto 25, 00185 Roma, Italy <sup>b</sup>DICII, University of Rome "Tor Vergata", Viale del Politecnico 1, 00133 Roma, Italy

## Abstract

We present a new approach to Parallel Discrete Event Simulation (PDES), where we enable the execution of so-called *cross-state events*. During their processing, the state of multiple concurrent simulation objects can be accessed in read/write mode, as opposed to classical partitioned accesses. This is done with no pre-declaration of this type of access by the programmer, hence also coping with non-determinism. In our proposal, cross-state events are supported by a speculative runtime environment fully transparently to the application code. This is done through an ad-hoc memory management architecture and an extension of the classical Time Warp synchronization protocol. This extension, named Event and Cross-State (ECS) synchronization, ensures causally-consistent speculative parallel execution of discrete event applications by allowing all events to observe the snapshot of the model execution trajectory that would have been observed in a timestamp-ordered execution of the same model. An experimental assessment of our proposal shows how it can significantly reduce the application development complexity, while also providing advantages in terms of performance.

*Keywords:* Discrete Event Simulation, Parallelization Techniques, Synchronization Transparency, Multicore Computing

# 1. Introduction

Traditionally, Parallel Discrete Event Simulation (PDES) has been based on the explicit partitioning of the entire simulation model into distinct simulation objects (or Logical Processes—LPs) [1] to be dispatched concurrently. Simulation objects' states are disjoint, and memory accesses during event processing are restricted to the state of the simulation object which is executing the event. Interactions across concurrent objects are only supported

Preprint submitted to Journal of Parallel and Distributed Computing

<sup>\*</sup>Corresponding Author

*Email addresses:* pellegrini@diag.uniroma1.it (Alessandro Pellegrini), francesco.quaglia@uniroma2.it (Francesco Quaglia)

by exchanging timestamped simulation events via messages. Proper synchronization mechanisms are used in order to ensure timestamp-ordered execution of events at each individual object, which is a sufficient (although not necessary [2]) condition for causal consistency.

Such classic approach fits traditional computing environments based on (large-scale) clusters of machines that embed loosely coupled CPUs. Indeed, partitioning the simulation model was the only feasible approach to exploit the computing power offered by this type of (distributed-memory) platforms, in order to speedup the execution of demanding applications.

More recent architectural trends slide towards multi/many-core technology. Here, the same physical memory is directly shared across a (large) set of tightly-coupled cores. This set can be large enough to provide an individual machine with the computing power needed to cope with demanding discrete event simulation models. This paradigm shift has driven the reshuffle of last-generation PDES platforms, in order to meet the peculiarities and potential of highly parallel shared-memory machines. Particularly, this has been done by relying on multi-threading, where all the worker threads operating within the PDES system share a common address space and can take care of executing simulation events scheduled to any object. However, literature proposals along this direction have been mostly focused on how to improve the runtime behavior of the PDES system via the optimization of *platform-level* tasks. Some of these proposals target the management of event exchange across simulation objects to the different worker threads depending on their actual computation demand (e.g. via load-sharing paradigms [5]).

Yet, none of these proposals had reflections on how PDES applications are actually coded. In fact, in the supported programming models each object still has its own disjoint state, and the execution of an individual event only allows to access the state of the destination object in data separation with respect to the other objects. In other words, no possibility is provided to access the state of multiple simulation objects, while atomically processing an individual event.

In this article, we introduce a new programming model to code PDES applications, along with the runtime support to make consistent their concurrent execution on parallel architectures. In this model, simulation objects can access, while processing any simulation event, the state of an arbitrary set of other simulation objects. In other words, our proposal augments the traditional PDES paradigm with so called *cross-state events*, which take place as atomic actions (potentially) touching in read and/or write mode any memory location currently associated with the memory image of any simulation object. The runtime support to handle cross-state events allows an effective exploitation of parallelism, since it supports the concurrent execution of both traditional and cross-state events on a multi-threaded PDES environment.

The motivations behind our proposal already stand out in the literature. Several results exactly point to the importance of allowing shared access to the same data in PDES systems while concurrently processing events at different simulation objects (see, e.g., [6, 7]). In this sense, cross-state events avoid the burden to pass (large) data structures produced during the execution of some event at simulation object A as the payload of a newly-scheduled event destined to object B. Indeed, the data can be directly accessed (e.g. via pointers) from the state of object A while processing the scheduled event at the destination object B. This simplifies the job of the application programmer, avoiding the need to manually implement complex marshalling operation of the (possibly scattered) data to be sent as payload of the scheduled event.

Even more important, cross-state events allow to dynamically "cluster" different simulation objects at the logical execution point of a single event, so that application coding can be extremely simplified. This is because any activity (e.g. simulation-state transition) logically involving more that one object can be implemented in a single event handler, atomically accessing the states of all the objects involved in the cluster, rather than being partitioned into multiple activities that are coordinated via explicit event scheduling across the objects—this is what occurs in classic PDES, based on full state disjointness.

At the same time, guaranteeing a correct (i.e. causally-consistent) execution when dealing with cross-state events requires proper application-transparent synchronization mechanisms to be put in place, which we describe in this article. Overall, the contributions in this article can be summarized as follows:

- 1. We describe the methodology behind the fully-transparent runtime detection of crossstate events, involving any number of simulation objects. This is done taking as a reference x86-64 architectures running Linux, although the concepts can be easily adapted to different architectures and operating systems—all the architectural facilities which are exploited are available on most systems, nowadays. As it will be shown, the runtime identification of cross-state events is fundamental, when application-transparency is pursued.

- 2. We discuss a synchronization protocol for speculative (optimistic) PDES systems, which we name ECS (Events and Cross-State) synchronization, which takes into account both traditional and cross-state events. This protocol, which can be seen as an extension of classical Time Warp synchronization [8], allows the parallel run to behave in a way which is equivalent to one where all simulation events are processed in non-decreasing timestamp order at any individual simulation object they touch, while being allowed to access any valid memory location belonging to the state of the whole simulation model—namely, any memory location logically belonging to the state of some object. At the same time, our protocol allows to run simulation events destined to different simulation objects concurrently, still transparently to the programmer.

Both the cross-state event detection methodology and the synchronization protocol have been implemented<sup>1</sup> within ROOT-Sim (the ROme OpTimistic Simulator), an open source simulation library supporting the development and execution of PDES models relying on ANSI/ISO-C programming.

The remainder of this article is organized as follows. In Section 2 we briefly discuss the fundamentals of Time Warp synchronization for PDES. The management of cross-state

<sup>&</sup>lt;sup>1</sup>The source code is available at https://github.com/HPDCS/ROOT-Sim.

events and the ECS synchronization scheme are presented in Section 3. The results of an experimental assessment are provided in Section 4. In Section 5 we discuss related literature results.

## 2. Recap of Time Warp Synchronization

In this section, we briefly present the foundations of Time Warp synchronization. The interested reader is invited to find a more comprehensive discussion in [1, 8].

In PDES systems, each simulation object is associated with its own view of simulation time, known as *Local Virtual Time* (LVT), which is used to locally track the advancement of the computation along the logical-time axis. The execution of an event can mark an update to its state, and moves the LVT to the timestamp of the processed event. It is the responsibility of the underlying runtime environment to track changes of the LVT of some object when dispatching the event to be processed [1]. While processing some event, new timestamped events destined to any concurrent object can be generated and injected into the system. At the same time, state transitions caused by event processing at the different objects can occur concurrently.

Classical PDES correctness rules are based on enforcing non-decreasing timestampordered state transitions at the different simulation objects [1]. Under this enforcement, each simulation object in the system has a coherent view of the flow of logical time.

In the speculative (optimistic) approach to synchronization, also known as Time Warp [8], events are stored by the runtime environment into per-simulation-object event lists, each of which is logically partitioned into a *future-event list* and a *past-event list*. The future-event list stores events not yet processed, while the past-event list records already-processed events. Each simulation object is eligible for dispatching along some thread running within the PDES platform unless its future-event list is empty. Once dispatched, the object is allowed to process the minimum-timestamp event kept by its future-event list. Such an event is then moved to the past-event list.

In Time Warp, a simulation object is scheduled for execution without any safety verification of causal consistency of its next-to-be-processed event. Hence, timestamp-order violations might arise, since a simulation object may receive an event (produced by another object) with a timestamp lower than its LVT. If a timestamp-order violation is detected, all the events that were executed out of timestamp order are rolled back by the runtime environment—they are moved back from the past-event list to the future-event list. Also, the LVT of the object is pushed back to the timestamp of the last event executed in correct order, and the object's state is restored to its value prior to the timestamp order violation, which is achieved by either relying on traditional checkpointing methods (see, e.g., [9-11]) or by the means of reverse computing approaches (see, e.g., [12, 13]), where reverse versions of the event processing routines are executed when rolling back processed events.

For the classical scenario where simulation-object states are disjoint, restoring the system to a correct state entails restoring individual object states independently, with no risk of domino effect. In particular, if dependencies occurred due to the scheduling of some event between a rolling back object  $O_a$  and another one  $O_b$ , these dependencies are undone via so called *anti-events*<sup>2</sup>. More in detail, an anti-event is generated for each event injected in the system by  $O_a$  during the portion of the computation to be rolled back, and is used to retract the originally injected event. Upon the delivery of an anti-event associated with an already executed event by  $O_b$ , the recipient also rolls back. Instead, if the event has not yet been executed, the anti-event has the only effect to "annihilate" the originally injected event. This operation typically occurs within the runtime environment. After rolling back, any simulation object resumes the execution of the events from its future-event list.

A concept that is relevant to optimistic synchronization is Global Virtual Time (GVT), which is defined as the smallest timestamp among those of (i) unexecuted events already inserted into the simulation objects' event lists, (ii) events being executed, (iii) events/antievents in transit from source to destination. Since no simulation object can ever rollback to a logical time preceding the GVT [8], the GVT value indicates the commitment horizon of the speculative computation. It is used both to execute actions that cannot be subject to rollback, such as displaying of intermediate results [14, 15], and for recovering memory. Specifically, event buffers with timestamps lower than the GVT value will never be reused after a rollback, therefore the runtime environment can discard them from the past-event lists of the simulation objects. The same happens to obsolete state information, if any, maintained to support state recoverability. The action of recovering memory after GVT calculation is typically referred to as *fossil collection*.

As hinted, in our approach we target optimistic PDES platforms relying on the multithreading paradigm, which have been shown to provide a set of benefits and to support optimized resource usage policies (see, e.g., [4, 16–18]) when compared to the traditional counterpart where parallelization is achieved by running a set of single-threaded processes within the simulation platform. Hence, we target the scenario where multiple threads can take care of dispatching whichever simulation object for execution which takes place by simply calling an event handler, with proper input parameters, along that thread. It is still possible to rely on temporary binding schemes between objects and worker threads in order to cope with, e.g., locality and other performance-related aspects.

## 3. Cross-State Events

## 3.1. Outline

The programming model enabled by cross-state events allows to bypass state disjointness in event processing. This enriches the traditional PDES programming model significantly. We provide such a support fully transparently to the programmer, who is therefore allowed to design simulation models able to access memory locations within any simulation objects' state in read/write mode. The programmer is also provided with the illusion that memory accesses are performed as if the events were dispatched for processing in non-decreasing timestamp order. In other words, the event-handling routine can be coded under the assumption that any memory access it performs is related to the current simulation time of

<sup>&</sup>lt;sup>2</sup>An anti-event is a "negative copy" of the corresponding event, or of its digest.

the event dispatched for processing. This corresponds to the LVT of the simulation object targeted by the event. On the other hand, we still enable parallelism in the execution in combination with speculation.

To make the programming model clearer, we show in the code snippet below a C example of an event handler in a PDES model implemented by relying on cross-state events. The event handler takes control as a callback function invoked by the underlying PDES runtime library. As typical of PDES-style coding rules, this function has a set of input parameters: the identifier of the object (obj) for which event processing is taking place and the state base pointer (state) which is the address of the data structure starting from which the object is allowed to access any other dynamically-allocated buffer belonging to its state via pointers. It also takes the timestmap of the currently dispatched event, and the event payload.

| 1        | void ProcessEvent(object_id obj, state_t *state, time_t event_timestamp, event_payload_t event) {        |

|----------|----------------------------------------------------------------------------------------------------------|

| 2        |                                                                                                          |

| 3        | <b>char</b> *p, q;                                                                                       |

| 4        |                                                                                                          |

| <b>5</b> | p = event.reference;                                                                                     |

| 6        |                                                                                                          |

| 7        | q = *p; // reading the content of memory location pointed by the 'reference' field in the event payload  |

| 8        |                                                                                                          |

| 9        | p = q; $p'$ writing the content of memory location pointed by the 'reference' field in the event payload |

| 10       |                                                                                                          |

| 11       | }                                                                                                        |

|          |                                                                                                          |

1

This can result in a cross-state event because we find statements where in-place pointerbased accesses to memory occur both in read (line 7) and write mode (line 9). In the example, the target memory locations for the accesses are taken from the payload of an event that has been scheduled for the simulation object identified by obj. These memory locations might correspond to memory buffers included in the state of the object that generated the event, which can be different from the one which runs it, identified by obj in the code snippet. More generally, a cross-state event is a simulation event scheduled for some simulation object A, for which the corresponding processing steps lead to accessing in read/write mode the state of one or multiple simulation object(s) distinct from A.

This is an innovative programming model not supported by any literature proposal. Indeed, reference PDES systems (e.g. [19, 20]) allow the programmer to rely only on the base pointer to the state of the simulation object that is the target of the event (namely state) to implement memory read/write operations. Also, the above example shows how in our solution we do not require any annotation in the code of the event handler. In other words, the programmer does not need to discriminate whether a memory access will refer to the local state of the simulation object targeted by the event, or to some remote object. We do not impose/require any a-priori indication of whether some event scheduled by the PDES application is a cross-state one or not. Hence we rely (and enable) pure runtime tracking of the occurrence of such type of events while the PDES run is in progress. Overall, the support for the correct handling of the memory accesses is fully transparent in our proposal, thus masking to the application developer any complication related to the possibility for two different objects targeted by a cross-state event to be concurrently scheduled for execution along two different threads.

Our solution is therefore significantly different from shared-data management approaches

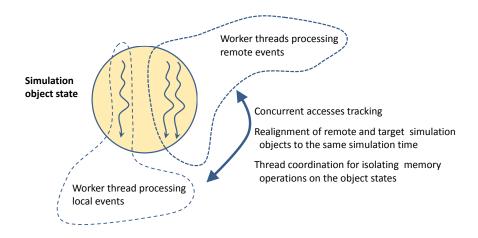

Figure 1: A scheme of state accesses to a simulation object with cross-state events.

like, e.g., Transactional Memory (TM), where code portions that might just potentially access the same data concurrently along different threads must be explicitly annotated. This is for example what happens when relying on the TM support offered by the gcc compiler.

Even more important, TM-style synchronization mechanisms to handle concurrent shareddata accesses are devised to achieve data consistency via isolation. Rather, a cross-state event does not only need to be managed via isolated accesses involving multiple objects along a same thread. It also needs to access object states that are aligned in simulation time to the timestamp of the cross-state event—namely, the LVT of the object processing the event. This is another reason for common TM support to be unsuited for the purpose of speculative PDES with cross-state events.

In Figure 1, we provide a schematic representation of the capabilities of the approach we propose. As depicted, we enable a single simulation object to advance in simulation time (still according to a speculative scheme), and to be the target of concurrent threads' memory operations. One of these threads is in charge of dispatching events destined to that simulation object—the simulation object is currently bound to that thread. These events are denoted as "local events" in the picture. On the other hand, other threads in charge of dispatching other simulation objects can anyhow process some cross-state events that require to access the state of the former simulation object. These events lead to a kind of remote access by those threads. In our proposal we provide mechanisms allowing:

- A. the transparent runtime detection of remote accesses;

- B. the realignment of the state of the simulation object targeted by a remote access to the simulation time corresponding to the timestamp of the cross-state event that determines the remote access, and the correct operation of threads in their concurrent activities within the extended Time Warp synchronization involving cross-state events.

Point A is addressed via a PDES-oriented state management architecture that controls

the way memory is delivered to keep the states of the simulation objects, and performs operating system tasks enabling the PDES runtime environment to track those remote accesses caused by the processing of cross-state events. In our solution we deal with object states kept into the heap, although we do not explicitly consider Thread Local Storage (TLS). This is because the state of the simulation objects in modern and general-purpose multithreaded PDES systems is intrinsically not private to specific threads, since objects can be dynamically re-bound to different threads for load-balancing purposes (see, e.g., [21, 22]). Our state management architecture is presented in Section 3.2. Point B is dealt with via the extension of the Time Warp synchronization protocol, which we name ECS synchronization. This is presented in Section 3.3. We emphasize again that, although our proposal targets Linux systems on the x86-64 architecture, the concepts it is based on are general and valid for other systems and architectures.

An important point to emphasize is that the state management architecture we present only deals with accesses to virtual addresses, and is fully transparent to the actual physical placement of the virtual pages hosting the states of the simulation objects. This implies that literature optimizations for placing virtual pages onto physical frames can be combined with our support for cross-state events. Indeed, our integration of this support within the **ROOT-Sim** platform coexists with the NUMA (Non Uniform Memory Access) optimizations already present in this runtime library [23]. With respect to this point, we stress again that our state management architecture is not a competitor of literature proposals for optimizing memory accesses in PDES on multi-core machines (like for example the ones presented in [3, 20]). Rather, it is an orthogonal means to enable an application programming model that was not supported by any literature proposal. Overall, our primary objective is to provide the programmer with a flexible way to develop models, while still guaranteeing adequate performance by the parallel run.

## 3.2. Object States Management and Memory Access Tracking

In our state management architecture, virtual memory is destined for usage by any simulation object (e.g. for allocating buffers belonging to the object state) according to *stocks*. More in detail, when the object requests new memory buffers, the memory management architecture reserves an interval of page-aligned virtual memory addresses (the stock) via the standard mmap POSIX API. Memory allocation is supported to the application programmer via the standard malloc API, transparently redirected at compile/link time to a proper memory allocator—see Appendix A for details.

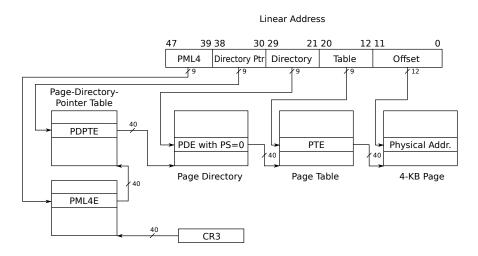

To understand how the stock abstraction can be used to track memory accesses related to cross-state events, let us consider the case of the IA32e paging scheme offered by x86-64 architectures—this is the paging scheme of x86-64 processors which is exploited by 64-bit versions of Linux. As shown in Figure 2, any 64-bit logical address has only 48 valid bits, which are used as access keys for a 4-level paging scheme, ultimately supporting pages of 4KB in size. The top level page table is called PML4 (or also PGD—Page General Directory) and keeps 512 entries. All the other page tables, operating at lower levels, also have 512 entries each.

Figure 2: The IA32e paging scheme with 4KB pages in x86-64 processors.

In our design, the stock of virtual memory pages used to allocate memory buffers for the state of a given simulation object corresponds to the set of contiguous virtual pages whose virtual-to-physical memory translation is associated with a single entry of the second-level page table, which is called PDP (Page Directory Pointer), and whose entries are referred to as PDPTE. Note that a single stock corresponds to  $512^2$  pages, for a total of 1GB of virtual memory. Hence, a single stock allows to manage object states up to 1GB of (dynamic) memory. On the other hand, reserving multiple stocks for a same simulation object will lead to manage object states reaching multiple gigabytes in size.

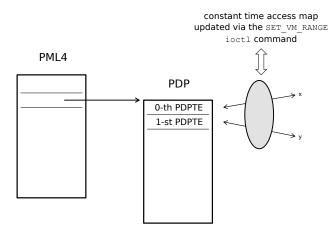

To interact with this memory management system, our architecture relies on a driver implemented into a Loadable Kernel Module for the Linux kernel. This driver creates a special device file which can be handled via ad-hoc ioctl commands supported by our driver. The SET\_VM\_RANGE command allows the driver to register the stocks to be reserved, and their association to the simulation objects (which are identified via classical unique numerical identifiers, as in typical PDES platforms). When this command is issued, the state of driver changes, and a kernel-level map, accessible in constant time, is set up. Here, for each reserved stock (logically related to one entry of a PDP page-table) the identifier of the simulation object destined to use that stock is recorded. In Figure 3 we show an example where a given PDP table has its 0-th entry (hence the corresponding stock of virtual memory pages) reserved for object x, and its 1-st entry reserved for object y.

Thanks to this organization, if simulation object x accesses any virtual address included in the stock reserved for object y, we know that such a memory access (which can be either in read or write mode in our execution model) is occurring outside the boundaries of its local state, and is actually involving the state of another object. Therefore, we are in the presence of a cross-state event.

The main problem to cope with to exploit the stocks as the means to capture whether the generic simulation object x (currently dispatched for execution along any worker tread, noted as  $WT_i$ , in the PDES platform) is involved in a cross-state event is related to how to determine that event processing gives rise to a memory reference falling outside the bound-

Figure 3: Example of association between stocks of virtual memory pages and simulation objects.

aries of the stocks currently reserved for object x. Classical memory protection mechanisms supported by the operating system (and related segmentation-fault handling schemes) are not suited for our purposes. Indeed, we cannot simply protect a-priori the accesses to stocks that are reserved for simulation objects other than x upon dispatching x along any worker thread  $WT_i$ . This is because these simulation objects might be requested to run concurrently with respect to x along other worker threads, which all share the same page table and experience the same protection rules as  $WT_i$ . Overall, preventing  $WT_i$  to access the stocks not reserved for simulation object x upon dispatching it (e.g. via the mprotect POSIX API) would lead to a change of the state of the page table so that any other thread would not be allowed to access those stocks. This definitely hampers concurrency, also leading to unneeded memory faults—by threads running objects other than x—in contexts where the object x does not require any access to "remote" stocks while processing the event.

Similarly, addressing the above problem via (user-transparent) code instrumentation would require to instrument memory-write<sup>3</sup> and also memory-read instructions. This would lead to (non-minimal) overhead to be paid even in case no cross-state access, although admissible, will ever occur—this renders the tracking of memory operations pointless on the side of synchronization tasks related to the management of cross-state events.

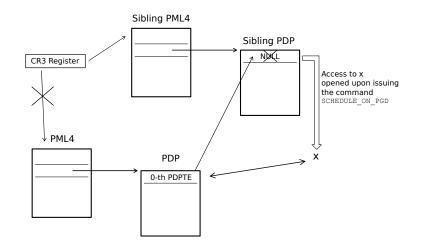

To cope with this issue, we have devised a memory management architecture where any worker thread  $WT_i$  is associated with a sibling PML4 page table, whose entries point to sibling PDP page tables. By default, the entries of the sibling PDP page tables, which are associated with the stocks that have been destined for usage by the simulation objects, are all set to NULL. This means that they do not allow to reach the lower-level page tables, hence not allowing access to any already allocated stock. Therefore, any attempt to access the stocks will lead to a memory fault. On the other hand, when  $WT_i$  dispatches simulation object x for event execution, the entries of the PDP sibling tables that correspond to the virtual-memory stocks destined for usage by x are "opened" to correctly allow the retrieval

<sup>&</sup>lt;sup>3</sup>This is typically done when supporting transparent incremental checkpointing in speculative PDES platforms [24, 25].

Figure 4: Example scenario where the memory stock associated with simulation object x is opened for access onto a sibling PDP page table.

of the lower-level page tables that contain the actual virtual-to-physical memory mapping (or tell that the pages are not present, e.g., they are swapped-out pages). This is done by copying the corresponding entries of the original PDP tables onto the destination entries of the sibling PDP page tables—see Figure 4 for an example scenario where the stock associated with simulation object x is again related to the 0-th entry of a given PDP page table. In our architecture, this operation can be executed via the ioctl SCHEDULE\_ON\_PGD command.

By using this command, the worker thread switches to what we refer to as *simulation-object mode*, where the only accessible stock is the one associated with the dispatched object (x in the example discussion), while the other stocks are not accessible in any way, given that their corresponding entries into the sibling PDP page tables are still set to NULL. As depicted in Figure 4, this operation also updates the CR3 register (namely, the page table pointer register in x86-64 processors). This allows to switch to the sibling PML4 for virtual-to-physical address resolution purposes.

Having different sibling PML4 tables, associated with the different concurrent worker threads, allows to concurrently dispatch and execute different simulation objects—this is done by having each worker thread open the access to the stocks associated with the object it is currently dispatching—while still having the possibility to determine whether any of the dispatched objects is keeping its memory references within its own stocks.

Two additional points must be discussed. First, having all the stocks closed for access by the worker thread, except the one(s) related to the dispatched object, leads (as noted before) to memory faults in case of a memory access to stocks other than open one(s), namely in case of the occurrence of a cross-state dependency across concurrent simulation objects. However, these faults cannot be tracked (and handled) via classical segmentationfault handling given that the "remote" stocks have already been validated via mmap, and the Linux kernel would simply lead the fault to reallocate the whole chain of page table entries for mapping the accessed virtual page in memory. This would bring the whole system into an inconsistent state where for the same virtual page multiple chains of page tables (and

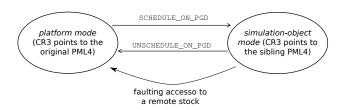

Figure 5: The state diagram for switch operations between original and sibling PML4 page tables.

thus physical frames) are present. This is something not directly handled by the Linux kernel, except if using invasive patches. To prevent this, when loading the external module, we also change the Interrupt Descriptor Table (IDT), directly accessible via the IDT register, to make the pointer to the page-fault handler point to a custom handler, rather than the original do\_page\_fault kernel function. If the fault is not related to accesses to remote stocks within the sibling paging scheme, then the original handler is invoked. Otherwise, the custom handler pushes control back to user mode in order to let the PDES platform actuate synchronization policies to handle cross-state events, as we shall discuss later when presenting ECS synchronization.

Upon a memory-fault occurring on sibling PDP entries because of cross-state dependency materialization, the faulting thread is put back into what we call *platform mode*, which implies that it is switched back to the original PML4. This is done to let this thread operate any memory access required to reconcile the execution of the concurrent objects according to ECS synchronization. This aspect will be treated in detail in the next section. On the other hand, if event processing at the currently-dispatched object ends, the worker thread can switch back to platform mode on demand—hence gaining again access to any memory location or data structure supporting the parallel execution—by using the ioctl UNSCHEDULE\_ON\_PGD command implemented within the driver. In Figure 5, we show the state diagram where the events causing the switch between simulation-object and platform modes are depicted.

Second, our architecture needs anyway to co-exist with the kernel scheduler, which poses issues on the side of managing the sibling PML4. Particularly, all the threads within a same Linux process share the same memory management information (the so called memory context), including the pointer to the original page table. This pointer is used by the kernel scheduler upon re-dispatching the thread after it has been context-switched off the CPU. Particularly, this pointer is reloaded into the page-table pointer register CR3 upon the occurrence of a context switch that gives control to the thread. However, if the thread was executing in simulation-object mode, CR3 would need to be filled with the address of the sibling PML4 (instead of the original page table).

Rather than providing a recompiled version of the kernel directly embedding a custom schedule function for correct management of the CR3 register (which would reduce the usability of our system), our Linux module adopts a *dynamic patching* approach based on the kprobe facility supported by Linux. It allows to inject an execution flow variation such that control goes to a schedule\_hook() routine in the module right before the kernel's sched-ule() function would execute its finalization part (i.e., stack realignment and return). In

this way, the actual final part of the scheduling process is under the control of our external module. The schedule\_hook() function simply executes the same return actions originally planned by the kernel's schedule() function. However, patching the original scheduler in this way allows the hook to take control when the decision about what thread needs to take control of the CPU-core<sup>4</sup> is already finalized.

The schedule\_hook() function implements the CR3 custom manager. This manager checks whether the CPU-scheduled thread is running into simulation-object mode (which can be done by checking per-thread meta-data that were setup via SCHEDULE\_ON\_PGD) and, in the positive case, it loads the sibling PML4 pointer into the CR3 register (thus persisting in the simulation-object mode when running the thread).

#### 3.3. ECS Synchronization

In this section we describe ECS synchronization, which ensures causal consistency for speculative PDES runs involving cross-state events. ECS synchronization has two goals. First, letting each simulation object process its events in non-decreasing timestamp order, in accordance with the reference correctness criterion for PDES platforms only entailing event dependencies. Second, allowing any cross-state dependency occurring at simulation time t—due to the occurrence of a cross-state event at that time—to let the involved object accessing remote stocks to observe the state snapshot that would have been observed at simulation time t in a timestamp-ordered run.

ECS synchronization can be seen as an extension of Time Warp synchronization based on the following two innovations:

- the introduction of temporary object blocking phases, which may lead to temporary block of the execution of an already dispatched simulation event at a certain object;

- the introduction of so called *rendez-vous events*, which are system-level events not causing updates on the destination object state, rather only driving block and unblock actions for processing activities at the concurrent objects. These are exploited to temporarily disable a simulation object to perform updates to its state along the simulation-time axis, given that its state snapshot is currently being accesses by a cross-state event (namely, it is involved in what we have referred to as a cross-state dependency).

#### 3.3.1. Rendez-vous Events

In our proposal, each simulation object x is associated with a cross-state dependency set which we refer to as  $CSD_x$ . It records the identifiers of all the simulation objects towards which x has materialized a cross-state dependency during the processing of a single event.  $CSD_x$  is initialized as empty upon dispatching object x for the execution of any new event, and gets possibly updated while processing this same event (if it reveals as a cross-state

$<sup>^4\</sup>mathrm{It}$  has actually already taken control of the CPU-core, since we are returning from the CPU-scheduling step.

one). ECS synchronization exploits the ad-hoc memory management architecture that we presented in order to detect that simulation object x is accessing a remote memory stock, namely the stock associated with object y, in either read or write mode, while processing its currently dispatched event  $e_x$ . The identity of the object towards which the cross-state dependency is being materialized (y in our example discussion) is also known, given that the custom memory-fault handler we designed, which pushes the faulting thread back in platform mode, notifies such an identifier into the thread user-mode stack. The memory fault occurrence gives rise to the following algorithmic steps:

- 1. The execution of  $e_x$  is temporarily suspended by having object x transitioning into a block state;

- 2. A rendez-vous unique identifier is generated and assigned to the event  $e_x$ , which we refer to as  $rvid(e_x)$ ;

- 3. A special rendez-vous event  $e_y^{rv}$  is scheduled for object y, marked with timestamp equal to the timestamp of event  $e_x$ , and with its identifier. We formally express this with the notations  $ts(e_y^{rv}) = ts(e_x)$  and  $rvid(e_y^{rv}) = rvid(e_x)$ .

Rendez-vous events are not generated by the application layer, rather they are platformgenerated events. Hence they do not have any associated processing rule at the application level. Nevertheless, ECS rendez-vous events are incorporated into the event list of the destination object (kept at the PDES platform level) as if they were traditional events, which is done for synchronization purposes.

Given that we are targeting speculative synchronization, a rendez-vous event may be a straggler event (if its timestamp is lower than the timestamp of some already processed event at the destination simulation object), thus possibly causing a rollback. Overall, rendezvous events need to be processed at the destination according to timestamp-order (possibly when resuming after a rollback), and the processing actions are platform-level ones given that, as hinted above, no application level processing rule is—and needs to be—specified for rendez-vous events in ECS.

When a simulation object y is dispatched for processing a rendez-vous event  $e_y^{rv}$ , ECS performs the following algorithmic steps:

- 1. Object y is put into a block state;

- 2. A special rendez-vous acknowledgment event  $e_x^{rva}$  is scheduled for object x, marked with no-timestamp but with the same rendez-vous identifier of  $e_y^{rv}$ , formally  $rvid(e_x^{rva}) = rvid(e_y^{rv})$ .

On the other hand, when the rendez-vous acknowledgement event  $e_x^{rva}$  is delivered to the destination simulation object x, ECS performs the following steps:

- 1. It inserts the identifier of the sender object, namely y, into  $CSD_x$ .

- 2. It unblocks the simulation object x so that it can be eventually re-scheduled along some worker thread (which can lead to resuming the execution of the originally-interrupted event  $e_x$ ).

object\_local identifier current\_rendez\_vous;

**upon** dispatching event  $e_x$  at object x **do**

- $CSD_x = \emptyset;$ 1.

- $current\_rendez\_vous_x = null;$ 2.

- $rvid(e_x) = null;$ 3.

${\bf upon}$  faulted access to the memory stock of object y by object  $x~{\bf do}$

1.  $e_x = get\_current\_event(x);$ 2. $\mathbf{if} \; (rvid(e_x) = null) \{$

3.  $mark = get\_unique\_id();$

4.  $rvid(e_x) = mark;$

- 5. }

- $e_{y}^{rv} = instantiate\_rendez\_vous\_event();$ 5.

6.

7.

8.

- 9.

- $current\_rendez\_vous_x = rvid(e_x);$ 10.block execution of object x;

**upon** dispatching rendez-vous event  $e_y^{rv}$  at object y **do**

- $source = get\_sender(e_y^{rv});$ 1.

- $e_x^{rva} = instantiate\_acknowledgment\_event();$ 2.

- $\begin{array}{l} \stackrel{\,\,{}_x}{rvid}(e_x^{rva})=rvid(e_y^{rv});\\ send \; e_x^{rva} \; to \; object \; x; \end{array}$ 3.

- 7.

- 8.  $current\_rendez\_vous_y = rvid(e_y^{rv});$

- 9. block execution of object y;

**upon** the receipt of the rendez-vous acknowledgement event  $e_x^{rva}$  at object x do

- $\mathbf{if} \; (current\_rendez\_vous_x \neq rvid(e_x^{rva})) \; \mathbf{\check{return}};$ 1.

- 2. $source = get\_sender(e_x^{rva});$

- 3.  $CSD_x = CSD_x \cup source;$

- 4. unblock object x;

**upon** ending the execution of event  $e_x$  at object x **do**

1.  $\forall k \in CSD_x$

- $e_k^{ub}$  send  $_x = instantiate\_unblock\_event();$ 2.

- $c_k$  schu x = instant $<math>rvid(e_k^{ub}) = rvid(e_x);$   $send \ e_k^{ub} \ to \ object \ k;$ 3.

- 4.

**upon** the receipt of the unblock event  $e_k^{ub}$  at object k do  $unblock \ object \ k;$ 1.

**upon** the resuming execution of object x after a block phase **do**

- $\forall k \in CSD_r$ 1.

- 2.open access to memory stock associated with k;

Figure 6: Pseudo-code for the management of rendez-vous events.

At this point, we know that simulation object y is blocked, thus not being currently allowed to process its events. Hence, the snapshot of its state is available to simulation object x for read/write operations, such as the operation that originally gave rise to the cross-state event's memory fault. However, upon re-dispatching object x (which leads to resuming the processing of  $e_x$ ), the involved worker thread cannot move into simulation-object mode by only opening the stock(s) associated with x into the sibling page tables. Indeed, we also need to open access to the stock(s) associated with object y. In our architectural support, this can be easily achieved via the SCHEDULE\_ON\_PGD command, since is allows to get a set of identifiers whose stocks need to be opened within the sibling page tables. In particular, when re-dispatching object x, the SCHEDULE\_ON\_PGD command is issued with the set  $x \cup CSD_x$  as input, which for our example discussion, contains the identifiers of both objects x and y.

The above algorithmic steps can be iterated in case cross-state dependencies are materialized towards multiple simulation objects while processing the event  $e_x$ , which will lead to the scenario where simulation object x can be rescheduled multiple times (while processing  $e_x$ ) with an incrementally enlarged set of open stocks. Once a remote memory stock (associated with a distinct object) becomes open for access by object x during the processing phase of event  $e_x$ , any access to this stock by x will not cause any additional memory fault while processing the same event.

To finalize the processing of  $e_x$ , we need to notify that the stocks associated with simulation objects towards which cross-state dependencies have been detected are no longer locked for access by object x. Hence, the owner simulation objects can resume their processing activities. This is done through the following steps, carried out at the end of the execution of  $e_x$  at object x:

- 1. an unblock-event  $e_k^{ub}$  is sent towards any object k whose identifier is in  $CSD_x$ . These events are again not marked with a timestamp, but with the rendez-vous identifier of the event  $e_x$  originating the cross-state dependency;

- 2. upon the delivery of  $e_k^{ub}$ , the recipient simulation object is simply put back as ready for being dispatched (hence exiting the block state).

In Figure 6, we report the pseudocode for the management of rendez-vous events. Two important notes. First, an event which generates a rendez-vous keeps the same rvid mark for all the possibly additional rendez-vous it will generate, in order to have a unique logical identifier for the rendez-vous, independently of the actual group of participating objects. Second, when a rendez-vous is triggered by some object x, the rvid value is recorded in the per-object variable  $current\_rendez\_vous$ , so that if a rendez-vous acknowledgement is received with an rvid value that does not match the current one seen by the simulation object, then the processing of the acknowledgement is simply skipped. This is related to the management of rollbacks in the speculative run, which we discuss in the next section.

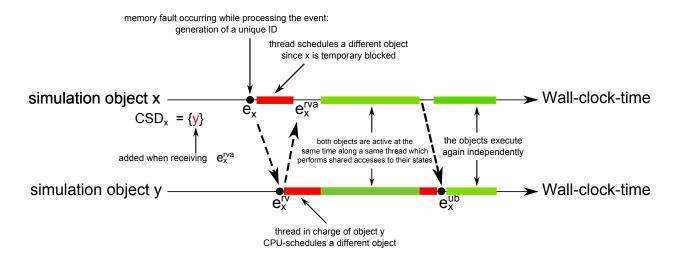

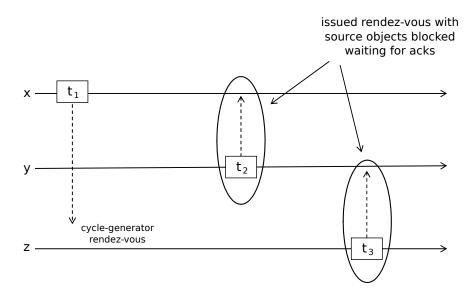

In Figure 7, we show a timeline illustrating how ECS manages a cross-state event  $e_x$  processed by simulation object x. With no loss of generality, the represented scenario refers to the case of two objects involved in the cross-state event, which are handled, in terms of CPU-dispatching, by different threads operating within the PDES system. The red bars indicate the wall-clock-time intervals along which the simulation objects x and y involved

Figure 7: An example time-line of ECS

in the rendez-vous are blocked. Object x is blocked up to the point in time where the state of object y is ready for being consistently accessed by the thread that processes the event  $e_x$ . In the meanwhile the thread in charge or processing the events destined to object y can CPU-schedule some object different from y. After the event is processed, object y stays blocked again up to the receipt of the ECS unblock event  $e_x^{ub}$ . Afterwards, both the objects can proceed processing their events concurrently along different threads. Clearly, in a scenario where the cross-state event hits a simulation object that is handled by the same thread that is processing the event, all ECS tasks are run along that same thread.

## 3.3.2. Dealing with Rollbacks

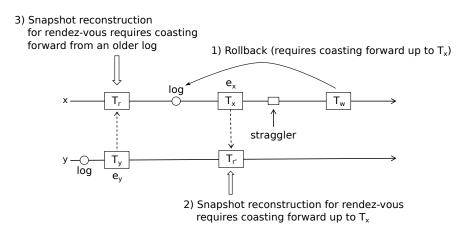

ECS targets speculative processing, where object blocking is never caused by native event dependencies, rather by the need for executing memory read/write operations in multiple stocks as an atomic action (within a rendez-vous). Thus, some care must be taken when handling rollbacks. In particular, when we process an event  $e_x$  that gives rise to a rendez-vous event  $e_y^{rv}$ , we need to define rules to handle the rollback of either object x or object y at a simulation time  $t' < ts(e_x)$ —or equivalently  $t' < ts(e_y^{rv})$ . The peculiarity of this scenario is related to fact that  $e_x$  and  $e_y^{rv}$  are both causally related to each other. Particularly, if  $e_x$  is rolled back, then we need to rollback  $e_y^{rv}$  given that object x may have performed updates on the memory stocks destined to keep the state of simulation object y while processing  $e_x$ . On the other hand, the processing outcome of  $e_x$  is affected by values possibly read by object x from the stocks destined to y at time  $ts(e_x)$ . If these values change due to a rollback of object y at a simulation time preceding  $ts(e_y^{rv})$ , the updated values should have been observed while processing  $e_x$  by object x.

To handle such a mutual dependency, we devise the following scheme. When the event  $e_x$  is rolled back, we simply send a classical anti-event for the rendez-vous event  $e_y^{rv}$  that was scheduled while processing  $e_x$ . Given that  $e_y^{rv}$  was incorporated into the event list of the destination object y, the arrival of the anti-event gives rise to a classical annihilation that

possibly rolls back y to the latest processed event with timestamp less than  $ts(e_y^{rv})$ .

The only additional aspect to consider is the effect of the rendez-vous anti-event on the destination object y in case it is still locked in the original rendez-vous. This scenario may occur because the source object x may experience a rollback leading to squashing the currently issues rendez-vous—this might be requested for progress of the run. In this case, no unblock event will be notified to y, and the effects of receiving the anti-event will be exactly that of pushing y out of the block state, as if the unblock event for the rendez-vous were received.

On the other hand, if the rollback is originated on object y, and pushes it to a simulation time less than  $ts(e_y^{rv})$  (which leads to undoing the execution of  $e_y^{rv}$ ), the following actions are taken. A special rendez-vous-restart event  $e_x^{rvr}$ , marked with the original rendez-vous identifier  $rvid(e_x)$  is sent out towards object x. This special event annihilates the processing of the original instance (while not removing it from the input queue), which leads to ultimately undoing  $e_y^{rv}$  via an anti-event. When processed after the rollback,  $e_x$  will generate a new instance of rendez-vous marked with a new unique identifier, so no mismatch will occur in any annihilation phase for rendez-vous events associated with different incarnations of their generating event. This also avoids cycles in the annihilation process.

Furthermore, all the other types of events used in ECS, such as acknowledgment and unblock events (see Figure 6), are not incorporated into the event lists of the simulation objects. Thus they are inherently ephemeral, and do not require particular care in the rollback scheme. Assuming FIFO communication across the objects (as can be typical of multi-thread PDES platforms [4]), these events can be simply discarded at the recipient side if the rendez-vous associated with their corresponding identifier (e.g.  $rvid(e_x)$  in case of the acknowledgement event sent to x upon the rendez-vous) is no longer in place.

Appendix B discusses correctness aspects of the presented ECS rollback scheme, particularly by the side of progress.

## 4. Experimental Study

## 4.1. Test-bed Platform

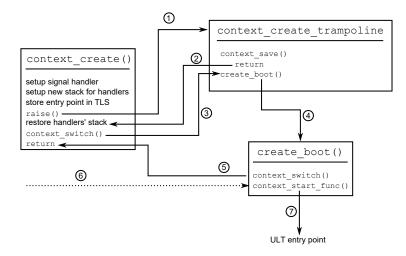

We integrated ECS within the open source ROOT-Sim package [26], particularly the symmetric multi-threaded version presented in [4]. A few relevant modifications to this simulation platform have been made for integration purposes. Most relevantly, we have created stack separation across the different simulation objects, by locating the stack of each object in the initial part of a stock of memory destined for object usage. This is done in a fully application-transparent manner. Further, execution resume in the different stacks, by also providing the correct processor and stack image, has been supported via modified versions of the setjmp and longjmp POSIX APIs. These ad-hoc APIs take into account the fact that an event can be theoretically descheduled at any memory-access instruction, including points which are not "safe" from a calling convention point of view. Further details on these aspects are discussed in Appendix C. They have also been used as the support to squash the stack when a rollback occurs while the simulation object is in the block state—this eventually leads the object to resume execution in a different context.

The application transparent facilities that have been used in our implementation to save and restore the states of the simulation objects are offered by the DyMeLoR library [25, 27], which has been integrated with the new memory management based on stocks. In particular, the memory segments from which DyMeLoR takes the chunks to be delivered for dynamic memory allocation by a given simulation object—and keeps the corresponding map for log/restore operations—correspond to the stocks of memory destined for that object usage. We recall that relying on DyMeLoR as actual memory allocator is fully transparent also by the side of memory management API since the application programmer is still allowed to use the classical ANSI/ISO-C memory allocation functions. In fact, in the ROOT-Sim architecture, these are transparently redirected to functions internal to DyMeLoR.

As for the (temporary) binding of simulation objects to threads, we still relied on the policies already supported in ROOT-Sim [22], which are aimed at optimizing the sharing of the overall simulation workload across the threads operating in the PDES system along the whole lifetime of the simulation run. The simulation objects currently bound to a given worker thread are dispatched according to the Lowest Timestamp First policy. However, when running with ECS, the simulation objects that are in the block state are not considered in the dispatching process (thus being again eligible for dispatching only after exiting the block state). In any case, the blocking of an object does not imply blocking the activities of the thread taking care of it, since this thread is allowed to dispatch other objects and/or to run platform-level tasks.

We have run experiments on a 32-core HP ProLiant server equipped with four 2GHz AMD Opteron 6128 processors and 64GB of RAM. Each processor has 8 physical cores that share a 12 MB L3 cache (6MB per each 4-cores set), and each core has a 512KB private L2 cache. The machine is equipped with 64 GB of RAM—organized in 8 NUMA nodes—and runs Linux 3.2. A ROOT-Sim configuration with 32 symmetric worker threads has been used in all the experiments, with GVT and fossil collection taking place each one second. We have not used more than 32 worker threads (so we have never exceeded the total number of physical cores) to avoid interference effects which could impair performance [28]. All the models used for the experimentation are available online in the ROOT-Sim repository.

#### 4.2. Experimental Data

This section is divided in two parts. We initially provide data for an evaluation of the overhead due to the core memory management facilities underlying cross-state events and ECS. To this end, we use a simulation model of a Personal Communication System (PCS) natively entailing disjointness of memory accesses by the different simulation objects—thus not exploiting at all ECS facilities, although paying the cost for the associated memory management support—which has been parameterized so as to achieve various runtime dynamics. After, we present data related to the assessment of the whole innovative approach to PDES—based on cross-state events—by relying on a multi-robot exploration model. In this part of the study, we also compare the runtime behavior of models exploiting ECS (implemented by relying on cross-state events) to the counterpart exclusively based on traditional PDES programming (only relying on event-dependencies via simulation objects' cross-event scheduling).

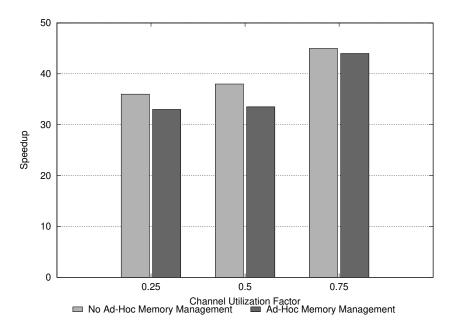

Figure 8: Relative speed-up by the parallel run without and with ad-hoc memory management vs the sequential run.

## 4.2.1. Pure Overhead Assessment

We evaluated the overhead induced by the memory management architecture supporting cross-state events by relying on a PCS model with 1024 wireless cells covering a square region, each one managing up to 1000 wireless channels. It models interference across different channels within a same cell and power management upon call setup/handoff in a high fidelity fashion according to the specification provided in [29]. This same model has been already used to assess the multi-threaded version of **ROOT-Sim** where we have integrated ECS, and its detailed description can be found in [30]<sup>5</sup>. Two specific aspects are relevant for this study: 1) each simulation object models an individual cell, and the interactions between objects exclusively take place via handoff events of mobile devices across different cells—hence, as hinted before, memory accesses while processing the events at the different simulation objects are intrinsically disjoint; 2) the average granularity (CPU requirement) of the events is directly proportional to the wireless channel utilization factor, since the more channels are busy, the more complex is the calculation of interference and Signal-to-Interference Ratio (SIR) while simulating power regulation.

We have run this model with three different configurations for the channel utilization factor, namely 25%, 50% and 75%, which gave rise to average granularity of the simulation events ranging from the order of 30 to 100 microseconds on the used computing platform. Also, we considered three different execution settings: a classical sequential execution (based on a calendar queue event scheduler), a parallel execution where no ad-hoc memory management facility is activated, and a parallel execution where we rely on the innovative memory

$<sup>^{5}</sup>$ The source code is anyhow available within the ROOT-Sim models' repository.

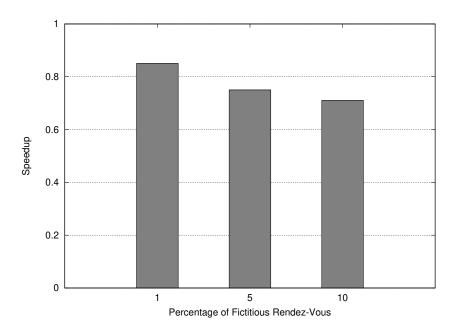

Figure 9: Relative speed-up by the ad-hoc memory management architecture vs the classical parallel run.

management architecture needed to support cross-state events and ECS. The latter setting entails switching between object-mode and platform-mode at each processed event—because of the need for managing the access to different memory stocks—with refill of the CR3 register and implicit squash of the TLB. This setting allows us to assess the pure mode-switch overhead operated by the support for ECS as evaluated in a scenario where ECS is useless since no cross-state event is ever detected in the native simulation model implementation.

In Figure 8, we show the variation of the speedup (vs the sequential run) we observed for simulating on the order of 1 million (committed) events in the different parallel execution modes (each sample is the average over 10 runs based on different random-generation seeds). By the data, we see how the maximal loss in performance by the ad-hoc memory management architecture switching between platform and object modes is on the order of 9% and is observed for the case of finer grain simulation events—namely, for the case of 25% utilization factor. Such a performance penalty almost disappears for coarser grain configurations.

Then, we modified the PCS model in order to generate fictitious cross-state events periodically. When one fictitious cross-state event occurs, the executing object simply performs a dummy read operation into the state of an adjacent cell. However, we do not really enable ECS synchronization, as the dummy read access is not important for the correctness of the simulation and can be executed out of timestamp order. Therefore, we only trap the access and open the stock associated with the object hit by the read operation. In this way we are able to assess the overhead induced by the identification at runtime of a cross-state event, when also including the management of memory faults and the activation of the ECS handler. For this experiment, we considered the PCS configuration with wireless channel utilization factor set to 50%, and we varied the frequency of occurrence of the fictitious cross-state events between 1% and 10% of the total number of events processed. In Figure 9, we show the relative speedup achieved by the configuration with ad-hoc memory management and fault handling upon the occurrence of fictitious cross-state events vs the configuration with no ad-hoc memory management. By the results, the ad-hoc architecture induces a speed-down that, as expected, increases with respect to the frequency of fictitious cross-state events. Note that the speed-down is not only caused by the overhead for handling the memory faults. It is also due to the switch between platform and object modes, which is mandatory in order to create the per-thread memory view needed to trap the access to the state of other simulation objects. However, the speed-down is quite limited for relatively infrequent fictitious cross-state events, and becomes non-negligible only when moving towards scenarios with relatively frequent cross-state occurrences (10% of the processed events).

On the other hand, the whole ad-hoc memory management architecture has been designed and realized to provide, transparently to the application code, a unique innovative support to handle cross-state dependencies in presence of concurrent objects. Hence the loss of performance in contexts where the model to be executed exhibits intrinsically disjoint accesses across different object-states (such as for the configurations in Figure 8) is the unavoidable price to be paid for the achievement of a runtime environment offering the above-mentioned level of transparency.

### 4.2.2. Effectiveness Assessment

To assess programmability and performance advantages provided by cross-state events and ECS synchronization, we have implemented a multi-robot exploration and mapping simulation model, according to the results in [31]. Specifically, a group of robots is set out into an unknown space, with the goal of fully exploring it. The map is constructed during the exploration, relying on the notion of *exploration frontier*. By keeping a representation of the explored world, the robot is able to detect which is the closest unexplored area it can reach, computes the fastest way to reach it and continues the exploration.

The robots explore independently of each other until one coincidentally detects another robot. Whenever two robots enter a proximity region, they perform three different actions:

- 1. they use their sensors to estimate their mutual physical position—recall that they are just in *proximity*;

- 2. they verify the goodness of their position hypothesis by creating a meeting point in the explored part of the region, and trying to meet again there;

- 3. if the hypothesis is verified, they exchange the data acquired during the exploration, thus reducing the exploration time and allowing for a more accurate decision of the actions to be taken.

If step 2 succeeds (i.e., the robots actually meet again), it means that the estimation of their respective position is correct. Therefore, they can form a *cluster* and start exploring the environment in a collaborative way. Specifically, this collaborative exploration can take place in two different ways. On the one hand, they jointly define (by relying on *cost* and *utility* functions, as defined in [31]) their next exploration targets, so that they can minimize the time required for a complete environment exploration. On the other hand, they might decide to make a *guess* about the position of other robots (the total number of which is

known) which are not part of the cluster yet. In the latter case, one of the robots (the one for which the utility/cost ratio is convenient) targets the hypothesized position. If a robot is found there, the aforementioned steps are carried out, so as to increase the knowledge of the environment.

When implementing a PDES simulation model for this scenario, three main hindrances are found. First, discovering the presence of a nearby robot can be difficult. In fact, either the robots must communicate to each other their current position—thus exponentially increasing the number of exchanged messages (events) which in turn can limit the performance of the simulation—or they have to notify it to specific simulation objects (i.e., the regions), again increasing the number of messages/events exchanged. Second, to estimate the respective position of the agents, various simulation events could be required. Third, exchanging map information could entail a data transfer non-negligible in size, posing a huge burden on the communication subsystem. Additionally, all these programmatic steps are not straightforward, as they force the modeler to reason according to the state-separation paradigm proper of PDES.

On the other hand, relying on cross-state events and ECS allows for a completelytransparent synchronization of the simulation objects involved in any mutual state update, which therefore simplifies the development process of the simulation model. In our implementation we rely on two different types of simulation objects, namely active ones (implementing the robots) and passive ones (implementing regions of the explored environment). More specifically, the environment is represented as a square region, divided into hexagonal cells. This choice allows us to define a meaningful mobility model for the agents, and at the same time allows us to define proximity regions which are used by the agents to detect the presence of other robots in the nearby. Also, periodic events occurring into any cell are envisaged as the basis for modeling the evolution (inside the cell) of any phenomenon characterizing the dynamic change in the state of the explored region.

At simulation startup, each passive simulation object creates random obstacles (which prevent the agents from reaching any neighbor cell), mimicking a rescue scenario where an open space is modified by an accident and the robots are used to explore it for rescue activities. At the same time, each passive object instantiates in its private simulation state (by relying on a standard call to malloc()) a *presence bitmap*. Each bit is associated with a specific robot, and its value is associated with the robot being in the cell or not. By relying on a fast bitmap scan, each robot (thus each active simulation object) is able to discover which robots are present in the cell. Finally, the passive object registers its simulation state by storing a pointer in a global array called states[], thus allowing any other simulation object to directly access (and/or modify) it. This is done by relying on a code block where the modeler is not required to rely on any platform-specific API, as illustrated in the following code snippet which is executed upon initializing the simulation model.

1 // Allocated state

```

8

state->neighbours[i] = -1;

9

} else {

state -> neighbours[i] = GetNeighbourId(me, i);

10

11

} else {

12

13

->neighbours[i] = -1;

state

14

15

// Allocate the presence bitmap

16

state - signature = malloc(BITMAP_SIZE(n_prc_tot - num_cells));

17

bzero(state->agents, BITMAP_SIZE(n_prc_tot - num_cells));

18

// Register the state in a global array. This is forbidden in traditional PDES

19

states[me] = state;

20

```

isValidNeighbour() tells whether a cell is placed on the boundary of the square region, GetNeighbourId() performs hexagonal-to-linear coordinates conversion for detecting a neighbour id, num\_cells is a variable defined by the model (and initialized at simulation startup by the user) which tells how many cells must be used to represent the square region, BITMAP\_SIZE is a model-defined macro which converts the number of agents to be represented into the bitmap to a number of sequential bytes providing the relative number of bits, n\_prc\_tot is a variable initialized at simulation startup which tells the total number of simulation objects in the current run, and me is a unique integer used to identify a specific simulation object, passed as input from the ROOT-Sim runtime environment to callbacks giving control to the application for event processing (as in most traditional simulation frameworks).

Thanks to cross-state events and ECS, when an agent enters a hexagonal cell (the id of the cell is piggy-backed on the event), registering its presence in the cell (which corresponds to a different concurrent object) is as simple as:

21 state->current\_cell = event\_content->cell;

25 cell->present\_agents++;

```

26 SET_BIT(cell->agents, me - num_cells);

```

Then, the agent has to collect information about the environment—which in our model is represented by the obstacles in the current cell—and has to detect the presence of additional robots. Since we have direct access to the cell's state thanks to cross-state events and ECS, this can be easily done by reading this information from it:

In case one robot is found in the cell, then the agent simply "merges" its view of the environment. This can be easily done by relying again on the **states**[] array, provided that each robot registers a pointer to its private state in it at simulation startup:

<sup>23 //</sup> Register the position of the robot in the cell. This is inconsistent in traditional PDES

<sup>24</sup> cell = (cell\_state\_type \*)states[state->current\_cell];

<sup>35</sup> robot = (agent\_state\_type \*)states[robot\_index];

No notion of parallelism is present in the shown code snippets from the simulation model, yet (by relying on cross-state events and ECS) the ROOT-Sim platforms is able to run the simulation model in parallel. We emphasize that the simulation model is written in an easy-to-manage style, without the need for respecting any PDES-related constraint, except for the signature of the event handlers, which is compliant with the one adopted by the ROOT-Sim platform.

To provide more details, ECS is triggered in different lines of the above code snippets. In particular, lines 25 and 32 trigger the synchronization with a cell (i.e., the current cell hosting the robot), while lines 37, 38, and 40 synchronize with another robot, namely one of the (possibly multiple) robots found to be in the cell. It is interesting to note that lines 25 and 32 access the state in different ways, the former being a read/write operation, the latter being simply a read operation. Similarly, line 37 accesses the state in read mode, while lines 38 and 40 entail writing multiple bytes of memory. Nevertheless, despite the multiple accesses, ECS requires executing the synchronization protocol (via rendez-vous events) only once per each other simulation object the state of which is being accessed while processing the current event.

As for runtime performance, we simulated a region of 4096 cells, and we changed the number of robot units moving around to 100, 500, and 1000. Higher values (500 and 1000 agents) give rise to average agent density into the explored space on the order of 0.12 and 0.24 per cell, respectively. Although these values might be above realistic settings, especially for cells modeling regions with non-minimal size, they help assessing how the performance of the ECS support for easy of programming and transparent parallelization scales vs variations of the ratio between the number of passive simulation objects (the cells) and the number of active ones (the agents). On the other hand, the configuration with 100 agents gives rise to an average density of per-cell agents of 0.02, realistically representing cases where, e.g., a reduced number of highly-specialized agents is employed for the exploration of a non-minimally sized region.

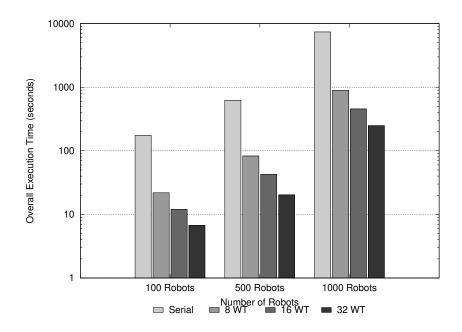

In Figure 10, we report the execution time of the simulation model for the three different cases, and for different amounts of ROOT-Sim worker threads (8, 16, and 32) deployed on top of the used multi-core computing system. We also report the execution time for running the very same application code sequentially, again on top of a classical calendar-queue scheduler. By the data we see how the parallel runs provide speedup that ranges between 30 and 35, which also linearly scales while varying the number of worker threads in the parallel simulation platform. This demonstrates the effectiveness of ECS in delivering adequate parallel performance, beyond providing supports for easy of programming. Also, the implementation patterns used in our model can constitute a reference for different scenarios entailing both passive (region) and active (agent) simulation objects.

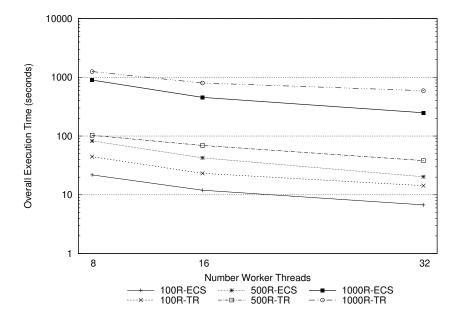

Finally, in Figure 11, we report performance data for a comparison between the above described ECS-based implementation of the simulation model, and one that exclusively relies on the classical PDES paradigm only performing fully disjoint accesses to the object states by the threads. In this variant, information sharing across the different objects while the simulation run proceeds is only based on events' exchange—the information to share at a given simulation time is piggybacked on the timestamped events as their payload. These exchanges take place whenever two (or more) robots meet in the map, and they have to merge their knowledge. In particular, every robot sends to any other robot in the justformed cluster an event piggybacking the information associated with the whole portion of the environment that has been explored so far. Upon processing such a message, a robot scans the payload and installs in its own private state all the information which is not present yet. In the plots, we refer to this implementation of the model as TR (Traditional), as opposed to the ECS-based one. For this comparative study we also vary the number of robots exploring the target area in the simulation ('R' in the plots) and the number of threads used to carry out the parallel runs. The reported data points still come from an average over 10 different runs, all executed with different random-generation seeds.

By the results, we can see that independently of the number of robots and the number of active worker threads, ECS-based synchronization provides a performance increase with respect to the traditional PDES run, which ranges from 19% to 58%. Anyhow, a more notable aspect is that when the number of robots increases, a more parallel execution—with increased numbers of worker threads—gives rise to a higher gap between ECS-based and traditional PDES. These phenomena are related to the fact that the event-exchange and the memory copy costs have a more prominent effect that is adverse to traditional PDES. On the other hand, ECS-based synchronization better scales with respect to both the model size and the used computing system power (number of CPU-cores). It is also important to emphasize that the variant of the simulation model based on traditional PDES requires much more code to be written by the simulation model's developer, which has also to manually implement some form of marshalling of the simulation state, in order to transmit its content as an event payload using the API of the underlying runtime environment. To provide a quantification of the benefits on programmability, we have that the ECS-based version of code has 25% less lines of code with respect to the traditional version not exploiting cross-state events<sup>6</sup>.

By the whole experimentation, we can conclude that cross-state events, and the associated ECS synchronization protocol, have the twofold benefit of delivering a non-negligible performance increase, anytime that the amount of data to be accessed across two objects is non-minimal, while enabling in any case a much simpler programming model.

## 5. Related Work

Several studies in the literature have been aimed at coping with the issue of state disjointness across concurrent objects in PDES systems, so as to allow some form of data (hence

<sup>&</sup>lt;sup>6</sup>Line counting refers to the versions of the two different models implementations available in the "models" branch of the ROOT-Sim respository.

Figure 10: Sequential vs parallel ECS-based execution times (log-scale on y-axis).

Figure 11: Traditional PDES vs parallel ECS-based execution times (log-scale on y-axis).